# SIGNETICS TWIN TESTWARE INSTRUMENT

# SYSTEM REFERENCE

# SIGNETICS TWIN TESTWARE INSTRUMENT SYSTEM

# REFERENCE

a subsidiary of U.S. Philips Corporation

Signetics Corporation 811East Arques Avenue Sunnyvale, California 94086 Telephone 4087 /39-7700

ORDER NUMBER: PRICE: TW09004000 \$5.00

Copyright October 1976, Signetics Corporation

Signetics Corporation reserves the right to make changes in the products described in this publication in order to improve design or performance.

Signetics Corporation claims trademark rights to the names TWIN and TWICE.

0 C 0 С 00

# TABLE OF CONTENTS

О.

| CHAPTER | TITLE                                                                                                                                                                                                                                                                                                                                                | PAGE                                                                                           |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 1       | INTRODUCTION                                                                                                                                                                                                                                                                                                                                         | 1-1                                                                                            |

|         | 1.0 INTRODUCTION                                                                                                                                                                                                                                                                                                                                     | 1-1                                                                                            |

|         | <ul><li>1.1 TWIN DEVELOPMENT SOFTWARE</li><li>1.2 PURPOSE OF THIS MANUAL</li><li>1.3 MANUAL CONTENTS</li></ul>                                                                                                                                                                                                                                       | 1–4<br>1–5<br>1–5                                                                              |

| 2       | SYSTEM DESCRIPTION                                                                                                                                                                                                                                                                                                                                   | 2-1                                                                                            |

|         | 2.0 SYSTEM ARCHITECTURE                                                                                                                                                                                                                                                                                                                              | 2-1                                                                                            |

|         |                                                                                                                                                                                                                                                                                                                                                      | 2-3<br>2-3<br>2-6<br>2-7<br>2-8<br>2-8<br>2-10<br>2-10<br>2-10<br>2-13<br>2-15<br>2-15<br>2-15 |

| 3       | MASTER CPU AND I/O BOARD                                                                                                                                                                                                                                                                                                                             | 3-1                                                                                            |

|         | 3.0 GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                              | 3-1                                                                                            |

|         | <ul> <li>3.1 OVERALL BLOCK DIAGRAM</li> <li>3.1.1 THE CPU</li> <li>3.1.2 I/O LOGIC</li> <li>3.1.3 INTERRUPT LOGIC</li> <li>3.1.4 DMA LOGIC</li> <li>3.2 DETAILED FUNCTIONAL DESCRIPTION</li> <li>3.2.1 2650 CPU</li> <li>3.2.2 I/O LOGIC</li> <li>3.2.3 INTERRUPT LOGIC</li> <li>3.2.4 DMA LOGIC</li> <li>3.2.5 BAUD RATE AND TIMER LOGIC</li> </ul> | 3-1<br>3-3<br>3-3<br>3-4<br>3-4<br>3-4<br>3-4<br>3-4<br>3-8<br>3-14<br>3-17<br>3-17            |

i

TABLE OF CONTENTS (con't)

| CHAPTER | TITLE                                                                                                                                                                                                                                                                                                                                   | PAGE                                                        |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 3       | MASTER CPU AND I/O BOARD (con't)                                                                                                                                                                                                                                                                                                        |                                                             |

|         | 3.3 UTILIZATION OF THE BOARD                                                                                                                                                                                                                                                                                                            | 3-17                                                        |

| 4       | PROM/RAM MEMORY                                                                                                                                                                                                                                                                                                                         | 4-1                                                         |

|         | 4.0 INTRODUCTION                                                                                                                                                                                                                                                                                                                        | 4-1                                                         |

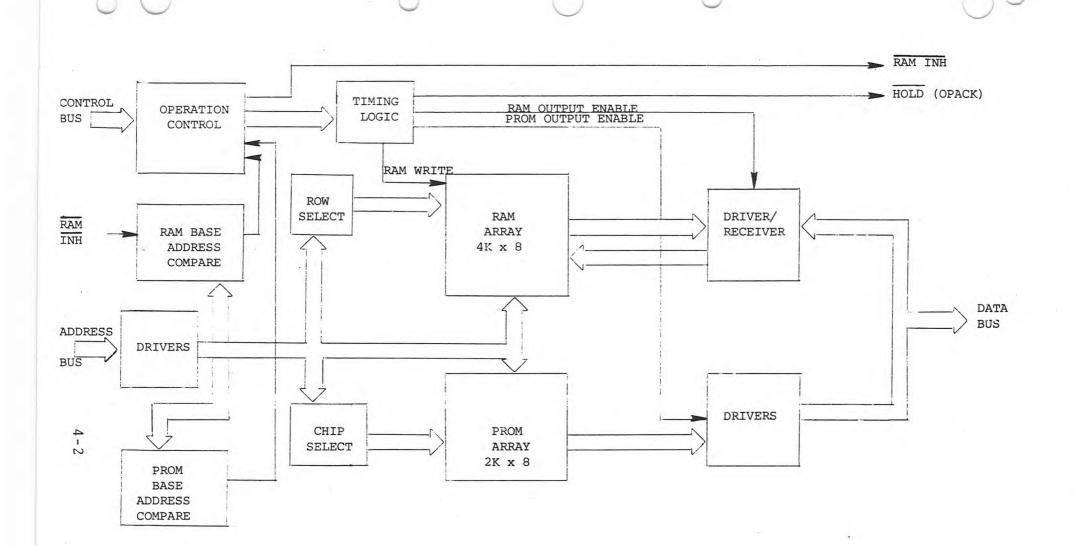

|         | <ul> <li>4.1 OVERALL BLOCK DIAGRAM</li> <li>4.1.1 RAM READ</li> <li>4.1.2 RAM WRITE</li> <li>4.1.3 PROM READ</li> <li>4.2 DETAILED FUNCTIONAL DESCRIPTION</li> <li>4.2.1 MEMORY ORGANIZATION</li> <li>4.2.2 MEMORY ADDRESSING</li> <li>4.2.3 TIMING</li> <li>4.2.4 -9 VOLT REGULATOR</li> <li>4.3 UTILIZATION</li> </ul>                | 4-1<br>4-3<br>4-3<br>4-3<br>4-3<br>4-3<br>4-4<br>4-4<br>4-4 |

|         | <ul> <li>4.3.1 SWITCHES AND JUMPERS</li> <li>4.3.2 RAM BASE ADDRESS SELECTION</li> <li>4.3.3 PROM BASE ADDRESS SELECTION</li> <li>4.3.4 RESIDENT PROM SELECTION</li> <li>4.3.5 OTHER JUMPERS</li> </ul>                                                                                                                                 | 4-5<br>4-6<br>4-6<br>4-7                                    |

| 5       | SLAVE CPU AND TWICE INTERFACE                                                                                                                                                                                                                                                                                                           | 5-1                                                         |

|         | 5.0 GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                 | 5-1                                                         |

|         | <ul> <li>5.1 OVERALL BLOCK DIAGRAM</li> <li>5.2 DETAILED FUNCTIONAL DESCRIPTION</li> <li>5.2.1 TWICE (User) and CPU SUPPORT LOGIC</li> <li>5.2.2 2650 ADDRESS AND DATA PATHS</li> <li>5.2.3 FORCED JUMP LOGIC</li> <li>5.2.4 SLAVE CPU PRIORITY INTERRUPT LOGIC</li> <li>5.2.5 MEMORY PROTECT LOGIC</li> <li>5.3 UTILIZATION</li> </ul> | 5-7<br>5-9                                                  |

ij.

#### TABLE OF CONTENTS (con't)

#### CHAPTER TITLE PAGE 6 RAM MEMORY 6-1 6.0 INTRODUCTION 6-1 6.1 OVERALL BLOCK DIAGRAM 6-1 6.1.1 RAM READ 6-1 RAM WRITE 6.1.2 6-2 6.2 DETAILED FUNCTIONAL DESCRIPTION 6-2 MEMORY ORGANIZATION 6.2.1 6-2 MEMORY ADDRESSING 6-2 6.2.2 6-3 6.2.3 TIMING 6:3 UTILIZATION 6-3 6.3.1 SWITCHES AND JUMPERS 6-3 6.3.2 RAM BASE ADDRESS SELECTION 6-3 OTHER JUMPERS 6.3.3 6-4 7 GENERAL-PURPOSE I/O BOARD 7-1 7.0 INTRODUCTION 7-1 7.1 GENERAL DESCRIPTION 7-1 7.2 DETAILED DESCRIPTIONS 7-3 7.2.1 SERIAL 1/0 PORTS 7-3 7.2.2 ADDRESS CONTROL 7-7 7.2.3 INPUT AND OUTPUT PORTS 7-7 7.2.4 INTERRUPT LOGIC 7-7 UTILIZATION 7.3 7-11 7.3.1 SWITCH SETTINGS 7-11 7.3.2 JUMPERS 7-11 7.4 SOFTWARE SUPPORT 7-13 7.5 INSTALLATION 7-20 8 PROM PROGRAMMERS 8.0 INTRODUCTION 8-1 8.1 **1702A PROGRAMMER** 8-1 8-1 8.1.1 CIRCUIT DETAILS 8.2 82S115 PROGRAMMER 8-5

iii

8.2.1 CIRCUIT DETAILS

## TABLE OF CONTENTS (con't)

| CHAPTER | TITLE                                                                                                                                                                                                                                                                                                                             | PAGE                                                 |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 8       | PROM PROGRAMMERS (con't)                                                                                                                                                                                                                                                                                                          |                                                      |

|         | 8.3 APPLICATION                                                                                                                                                                                                                                                                                                                   | 8-7                                                  |

| 9       | DEBUG AND FRONT PANEL I/O MODULE                                                                                                                                                                                                                                                                                                  | 9-1                                                  |

|         | 9.0 INTRODUCTION                                                                                                                                                                                                                                                                                                                  | 9-1                                                  |

|         | <ul> <li>9.1 GENERAL DESCRIPTION</li> <li>9.1.1 MASTER/SLAVE CONTROL</li> <li>9.1.2 DEBUG FEATURES</li> <li>9.1.3 I/O COMMANDS AND INTERRUPTS</li> <li>9.1.4 FRONT PANEL INTERFACE</li> <li>9.2 DETAILED DESCRIPTION</li> <li>9.2.1 MASTER/SLAVE CONTROL AND HALT DECTECTOR</li> <li>9.2.2 I/O COMMANDS AND INTERRUPTS</li> </ul> | 9-1<br>9-3<br>9-4<br>9-5<br>9-5<br>9-5<br>9-5<br>9-7 |

|         | 9.2.3 DEBUG FEATURES<br>9.3 UTILIZATION                                                                                                                                                                                                                                                                                           | 9 <b>-1</b> 2<br>9 <b>-1</b> 6                       |

| 10      | MOTHER BOARD AND POWER SUPPLIES                                                                                                                                                                                                                                                                                                   | 10-1                                                 |

|         | 10.0 INTRODUCTION                                                                                                                                                                                                                                                                                                                 | 10-1                                                 |

|         | 10.1 THE MOTHER BOARD                                                                                                                                                                                                                                                                                                             | 10-1                                                 |

|         | 10.2 POWER SUPPLIES                                                                                                                                                                                                                                                                                                               | 10-1                                                 |

|         |                                                                                                                                                                                                                                                                                                                                   |                                                      |

## APPENDIX

0

D

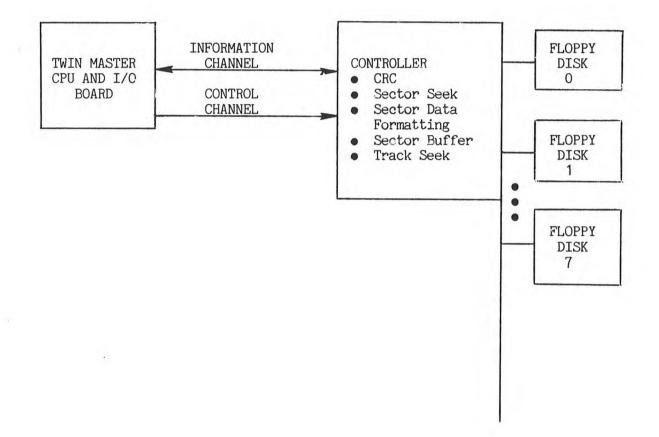

| Α | FLOPPY DISK CONTROLLER         | A-1          |

|---|--------------------------------|--------------|

| В | SERVICE REQUESTS               | B <b>– 1</b> |

| С | TELETYPE MODIFICATIONS         | C-1          |

| D | ADDING A DEVICE DRIVER TO SDOS | D <b>– 1</b> |

iv

| F | Ι | G | U | R | E |  |

|---|---|---|---|---|---|--|

|---|---|---|---|---|---|--|

TITLE

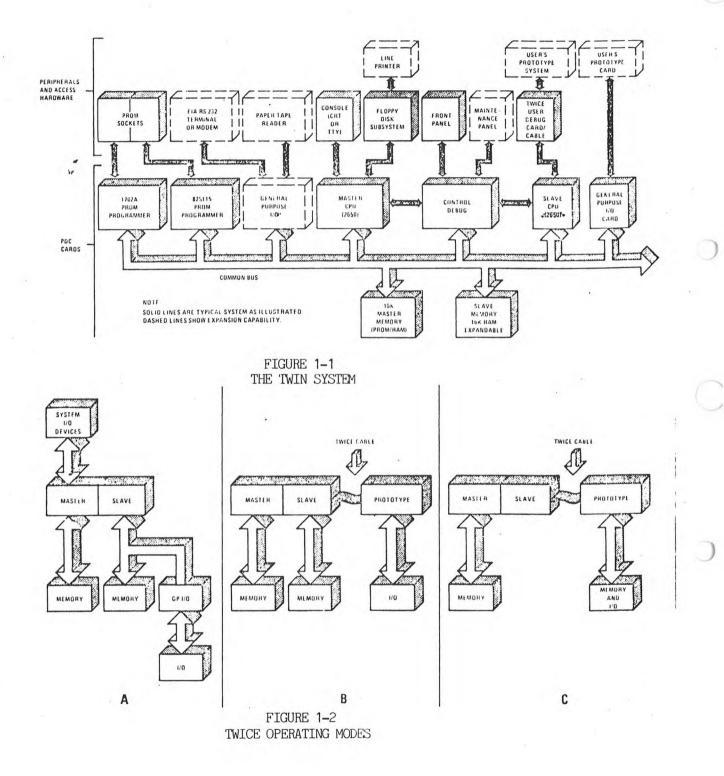

| 1-1<br>1-2 | THE TWIN SYSTEM<br>TWICE OPERATING MODES   |   | 1-3<br>1-3   |

|------------|--------------------------------------------|---|--------------|

|            |                                            |   |              |

| 2-1        | PROGRAM DEVELOPMENT COMPUTER BLOCK DIAGRAM |   | 2-2          |

| 2-2        | MEMORY ORGANIZATION                        |   | 2-4          |

| 2-3        | BUS STRUCTURE                              |   | 2-5          |

| 2-4        | MASTER CPU AND I/O                         |   | 2-9          |

| 2-5        | MASTER MEMORY                              |   | 2-11         |

| 2-6        | PROM PROGRAMMERS                           |   | 2-12         |

| 2-7        | SLAVE CPU AND TWICE INTERFACE              |   | 2-14         |

| 2-8        | SLAVE MEMORY                               |   | 2-16         |

| 2-9        | GENERAL-PURPOSE I/O                        |   | 2-17         |

| 2-10       | FRONT-PANEL I/O AND DEBUG                  |   | 2-19         |

| 3-1        | DATA FLOW BLOCK DIAGRAM                    |   | 3-2          |

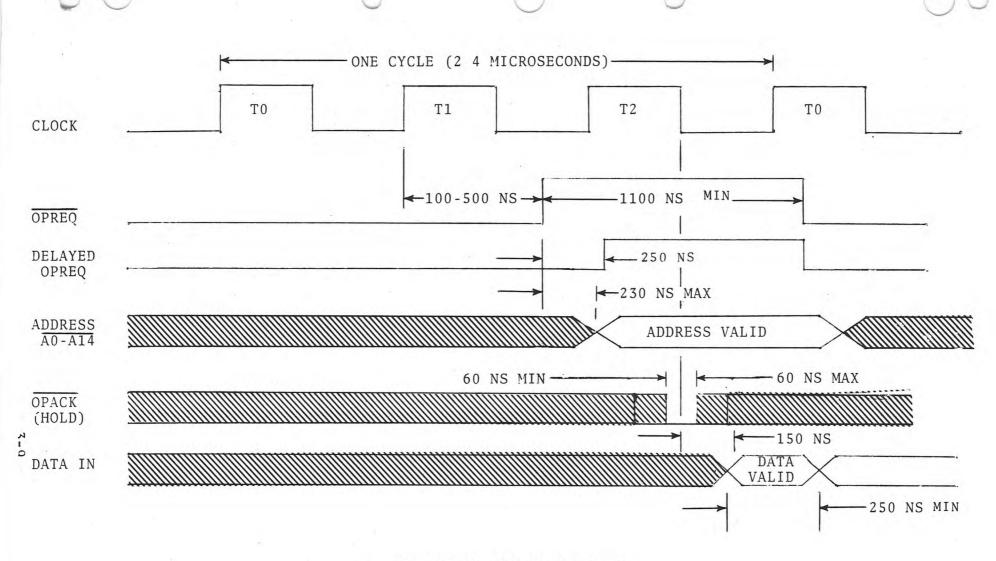

| 3-2        | CPU TIMING                                 |   | 3-9          |

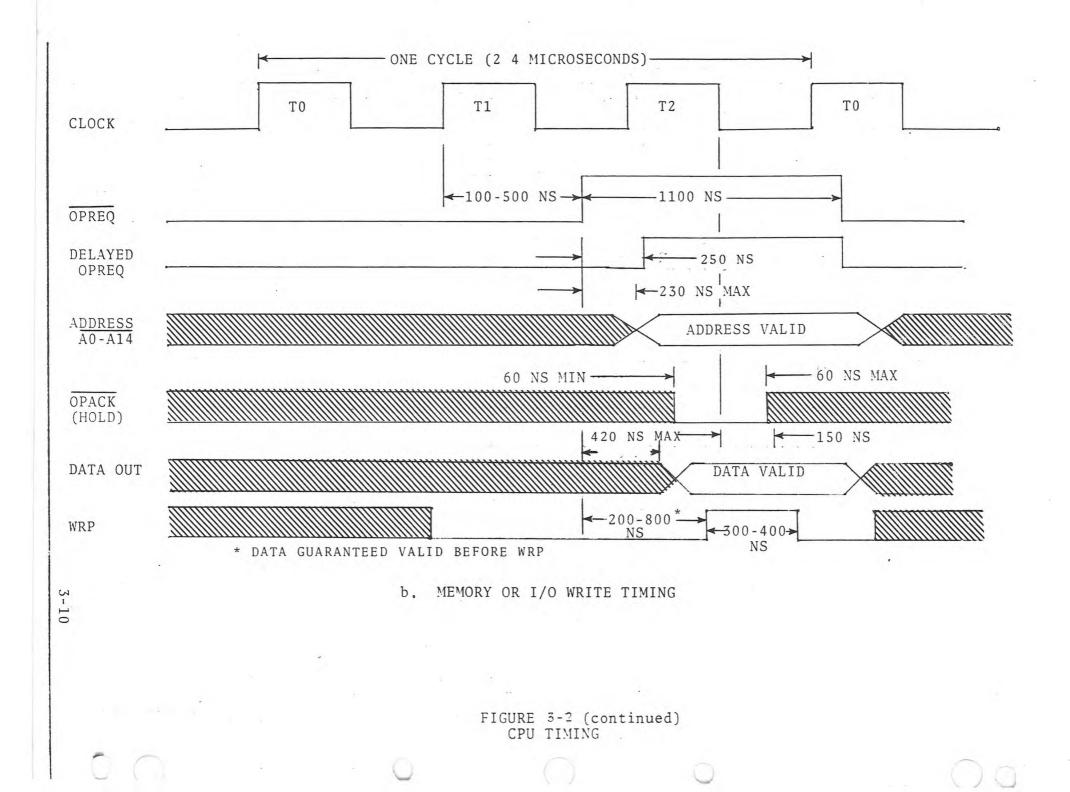

| 3-2        | MEMORY OR I/O WRITE TIMING                 |   | 3-10         |

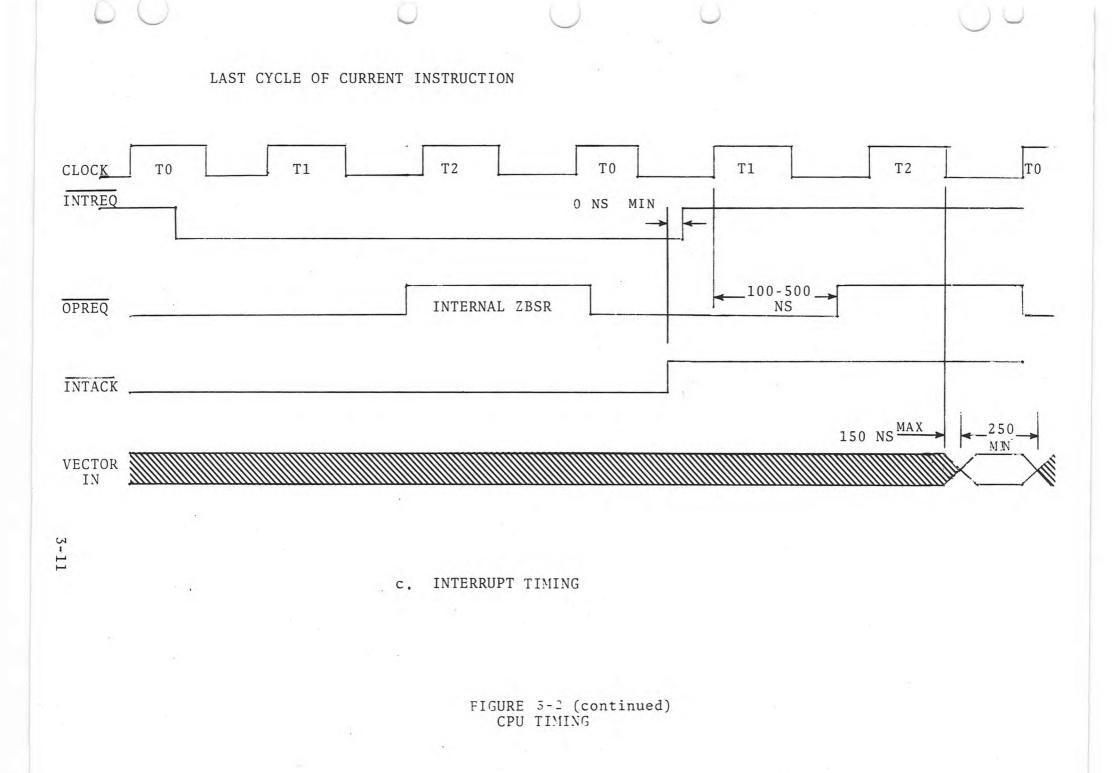

| 3-2        | INTERRUPT TIMING                           |   | 3-11         |

| 3-3        | TIMER STRAPPING DIAGRAM                    |   | 3-19         |

| 4-1        | PROM/RAM MEMORY BLOCK DIAGRAM              |   | 4-2          |

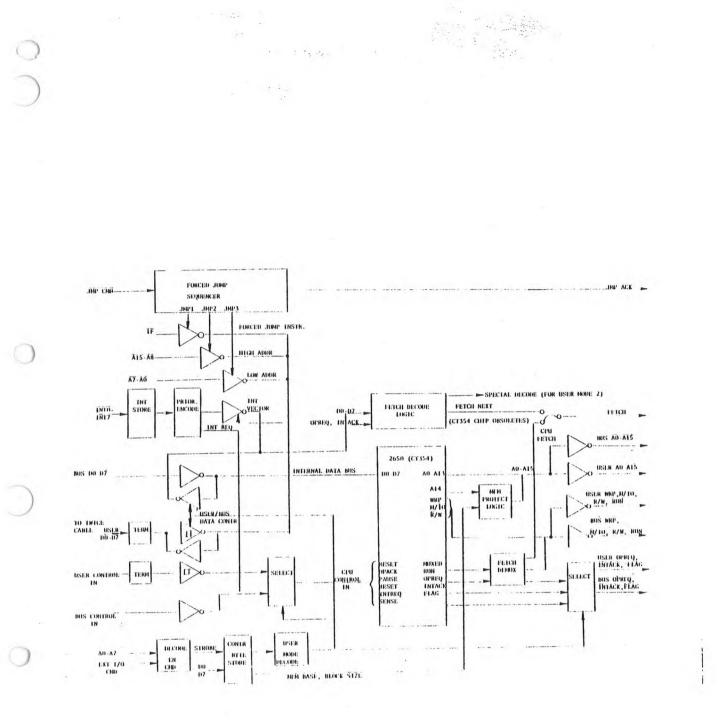

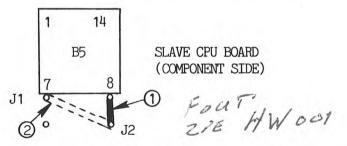

| 5-1        | SLAVE CPU AND TWICE INTERFACE              |   |              |

| 5-2        |                                            |   |              |

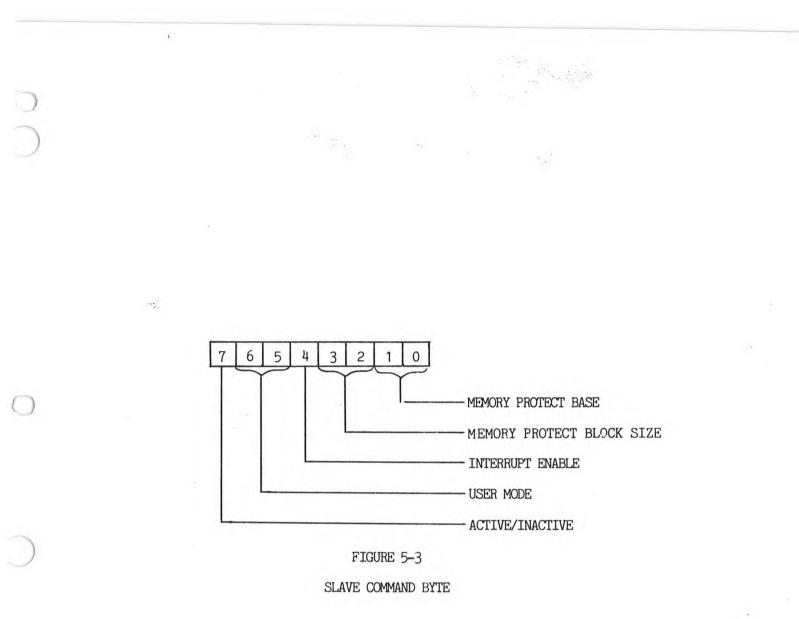

| 5-3        | SLAVE COMMAND BYTE                         |   | 5-5          |

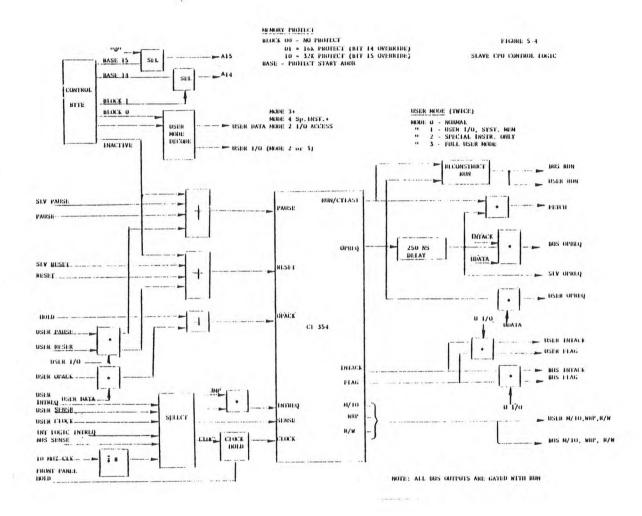

| 5-4        |                                            |   |              |

| 5-5        | CONTROL LINE MULTIPLEXING                  |   | 5-8          |

| 5-6        | RUN DEMULTIPLEX TIMING                     |   | 5-10         |

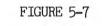

| 5-7        | JUMP SEQUENCER TIMING                      |   | 5-11         |

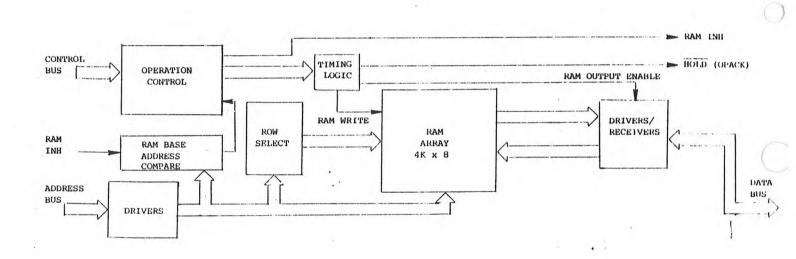

| 6-1        | RAM MEMORY BLOCK DIAGRAM                   | 4 | 6 <b>-</b> 5 |

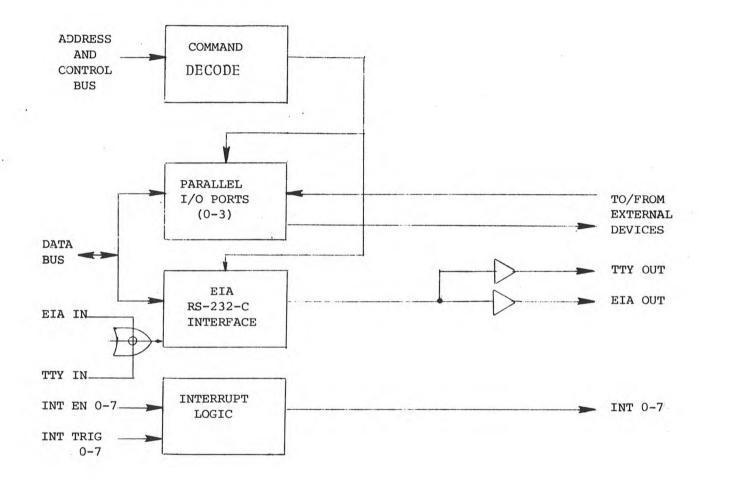

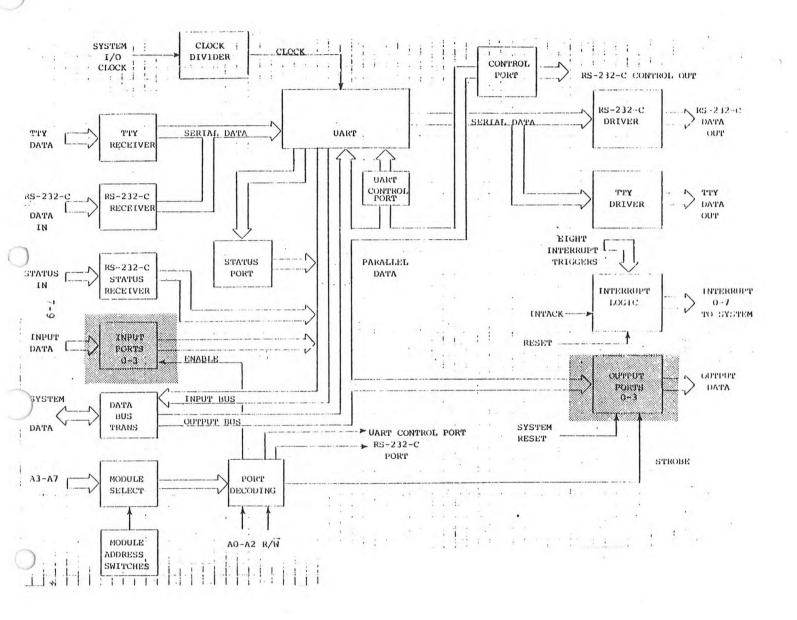

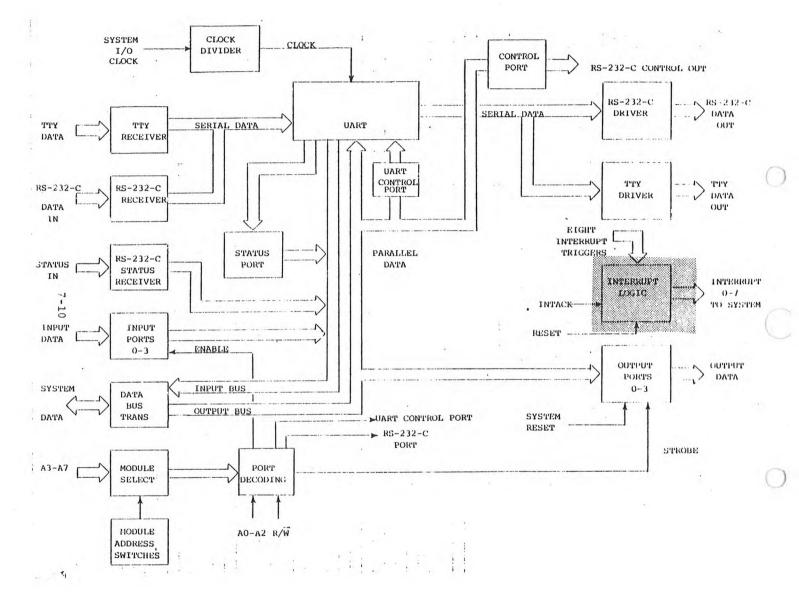

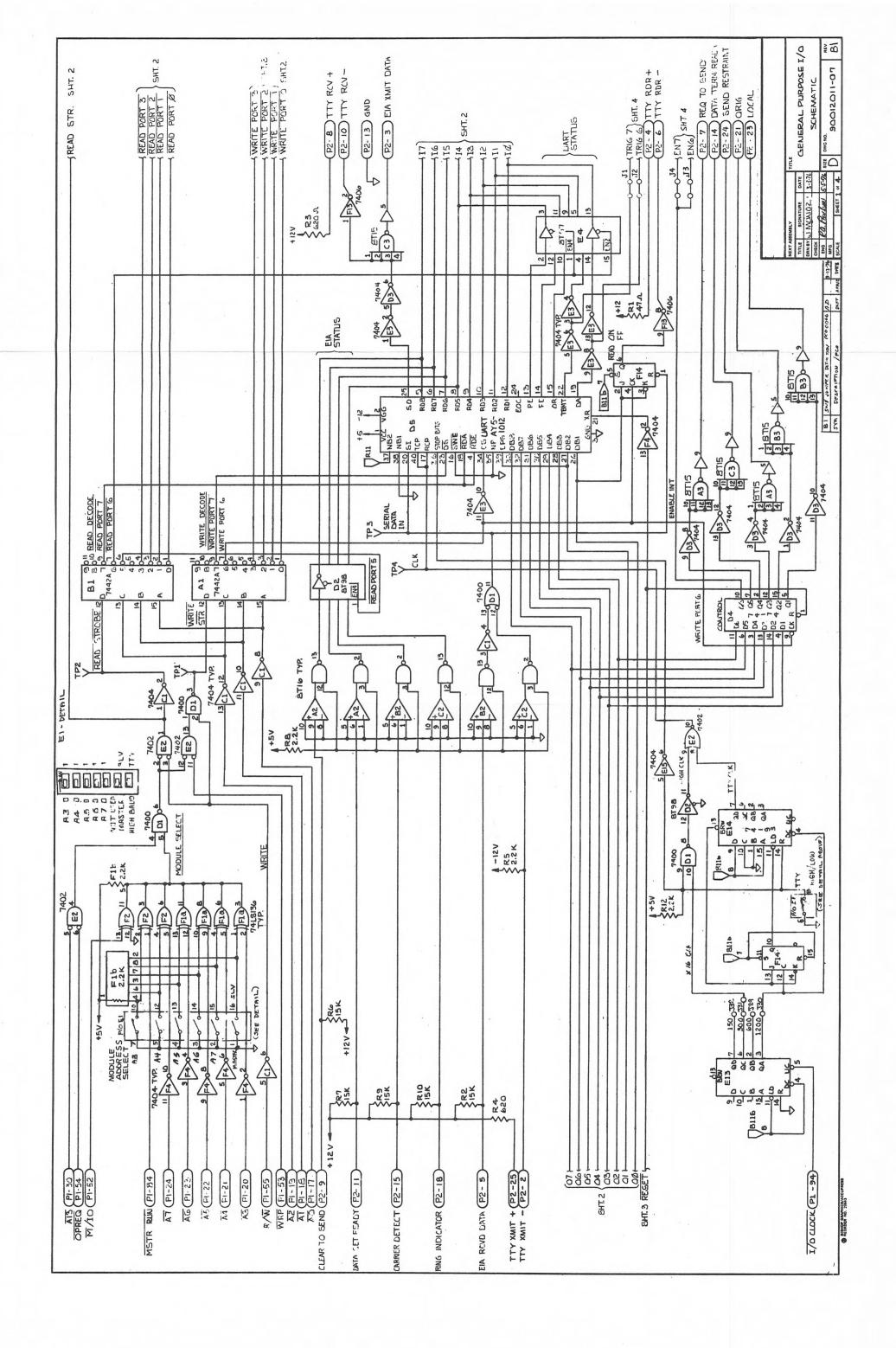

| 7-1        | SIMPLIFIED BLOCK DIAGRAM                   |   | 7-2          |

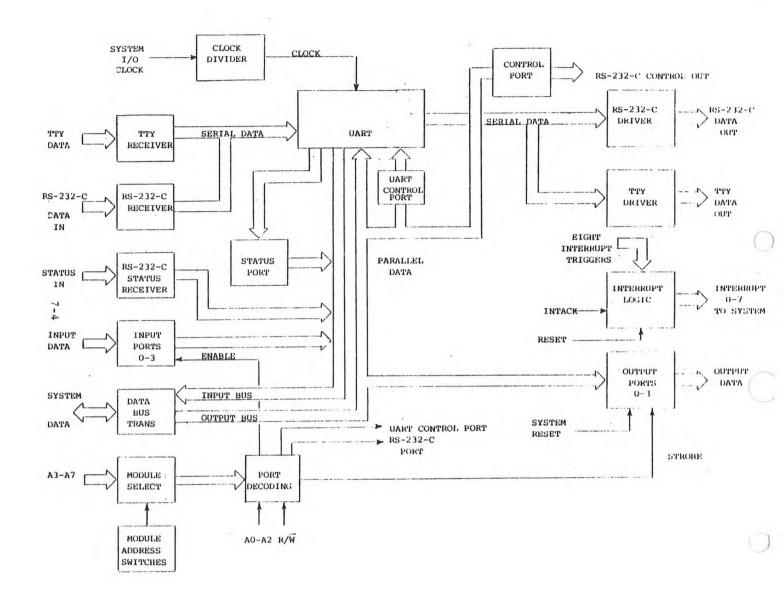

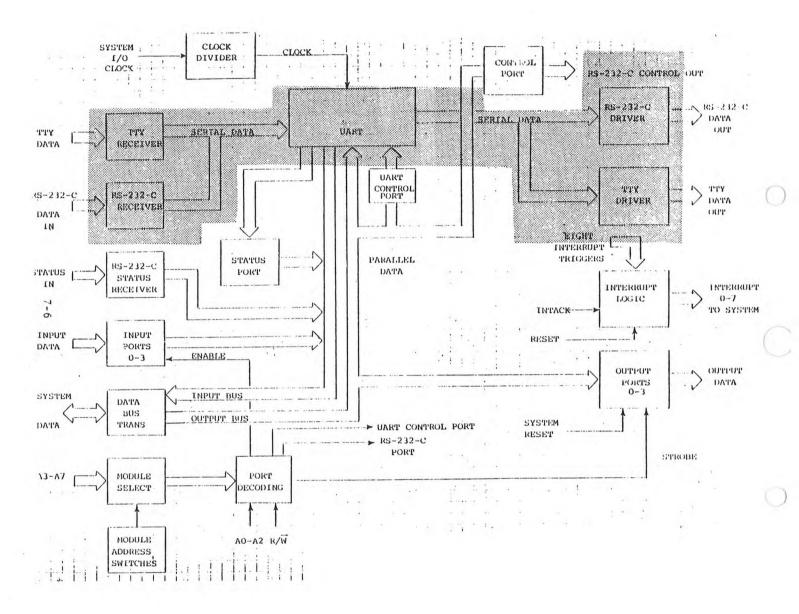

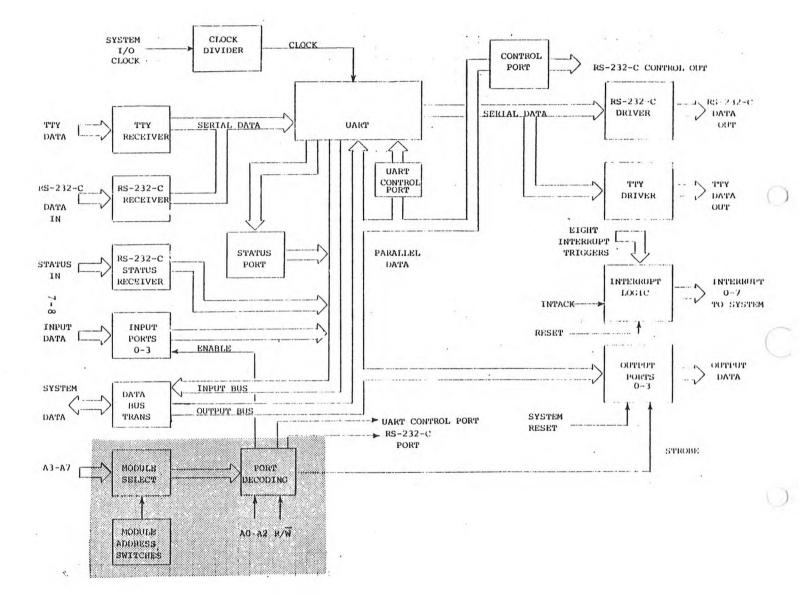

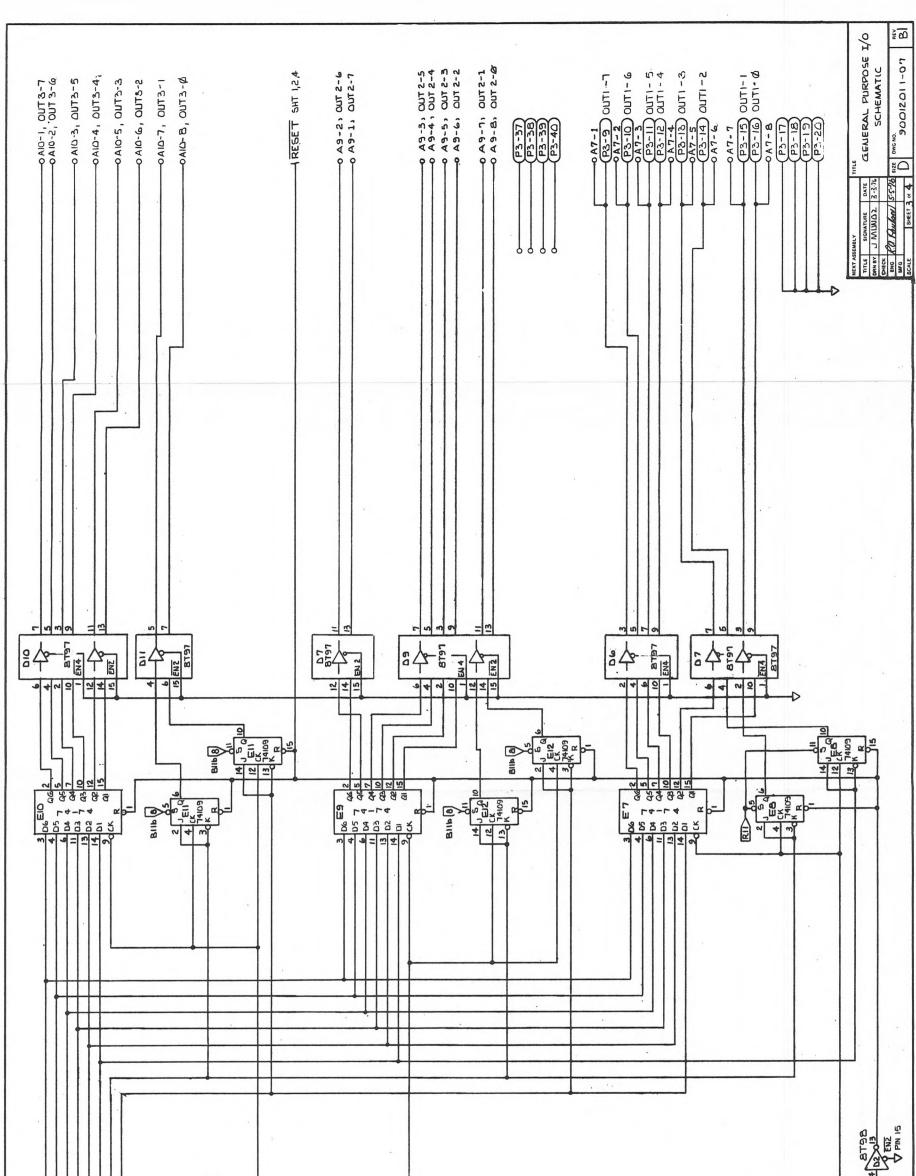

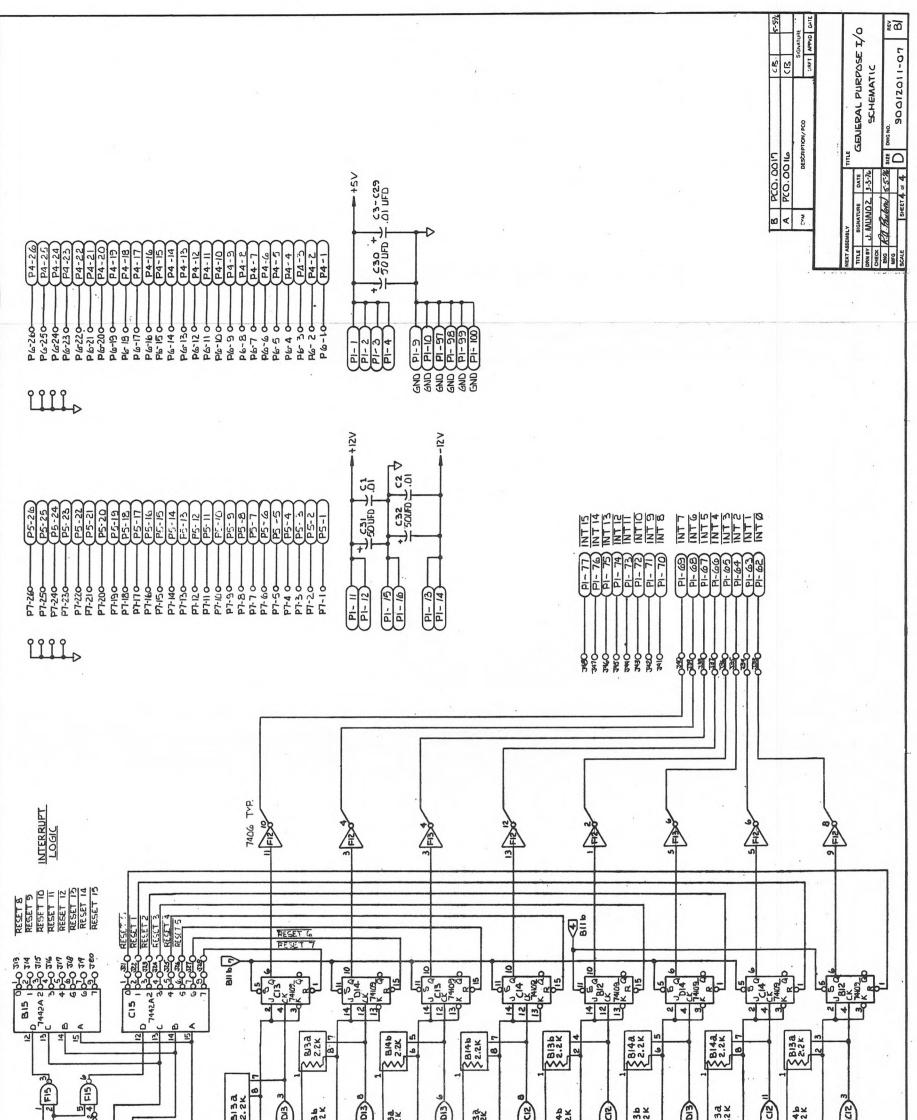

| 7-2        | OVERALL BLOCK DIAGRAM                      |   | 7-4          |

| 7-3        | SERIAL I/O PORTS                           |   | 7-6          |

| 7-4        | ADDRESS DECODING                           |   | 7-8          |

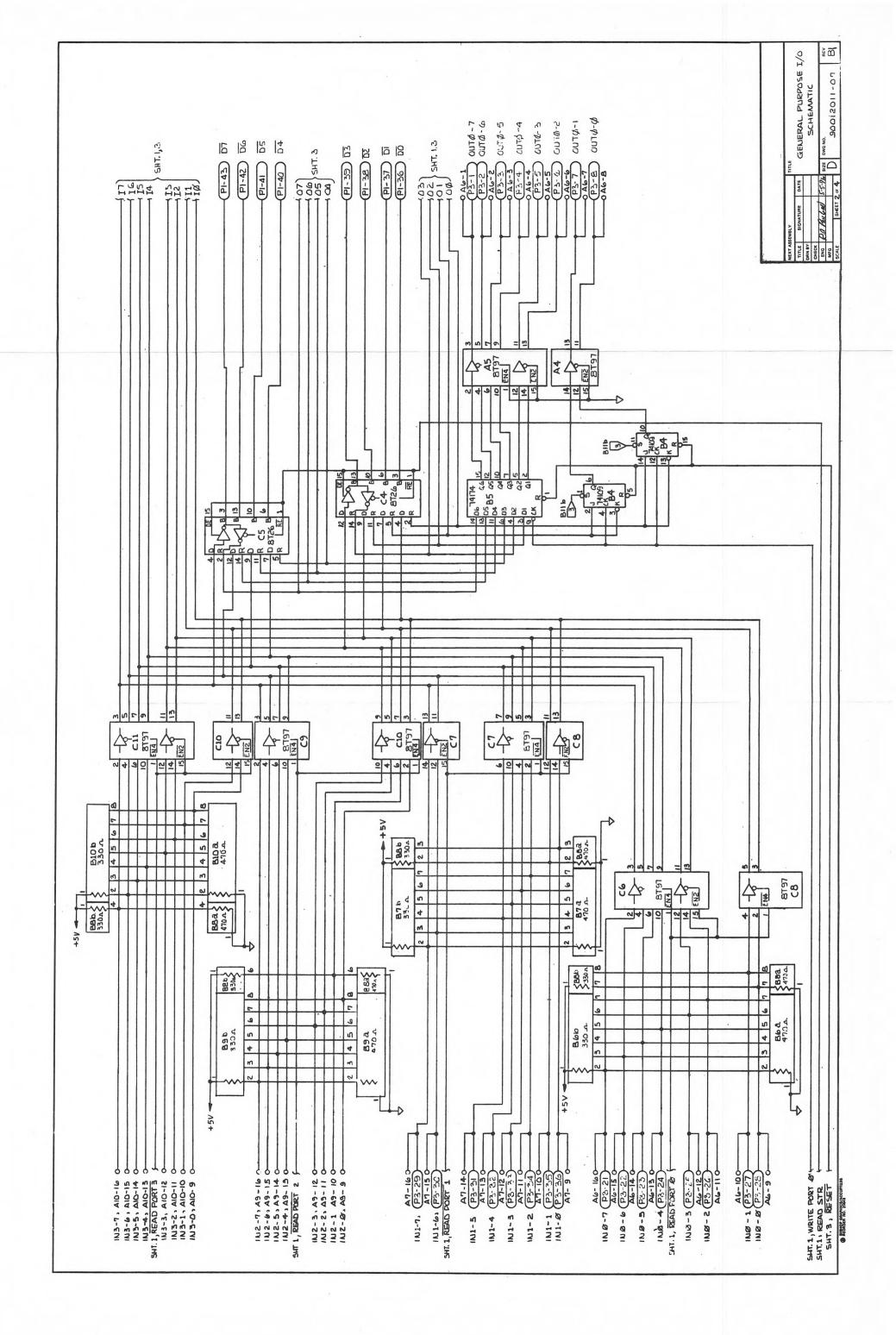

| 7-5        | I/O PORTS                                  |   | 7-9          |

| 7-6        | INTERRUPT LOGIC                            |   | 7-10         |

|            |                                            |   |              |

v

# FIGURE

TITLE

PAGE

3

0

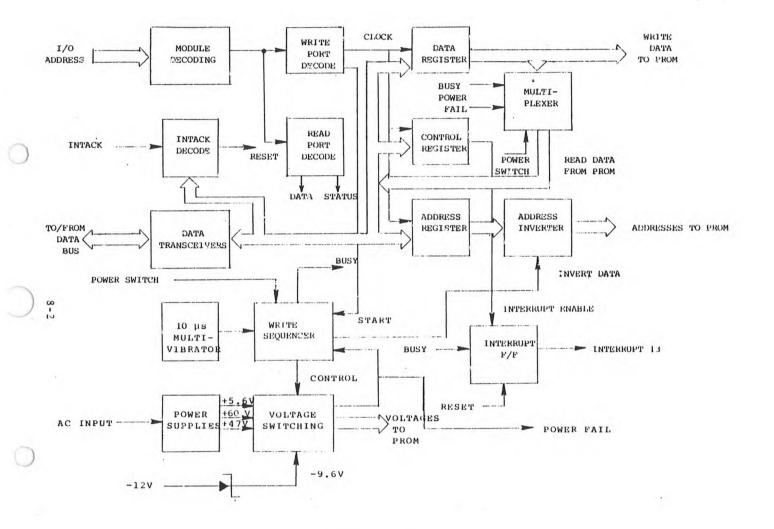

| 8-1 | 1702A PROGRAMMER BLOCK DIAGRAM          | 8-2  |

|-----|-----------------------------------------|------|

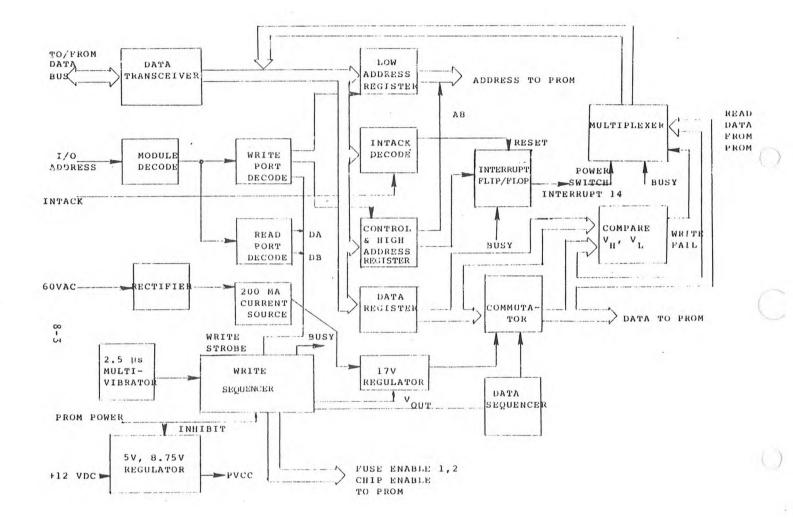

| 8-2 | 82S115 PROGRAMMER BLOCK DIAGRAM         | 8-3  |

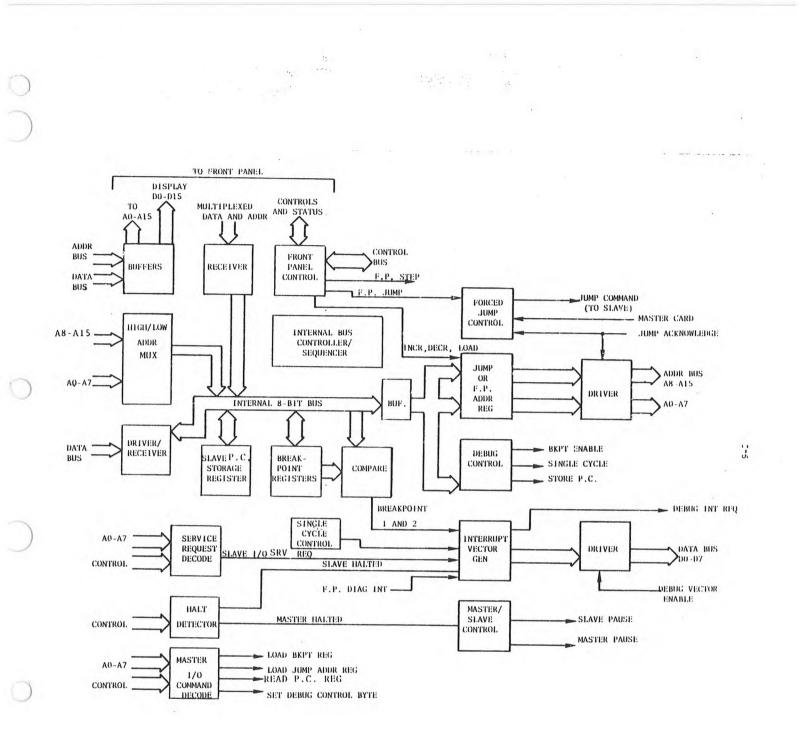

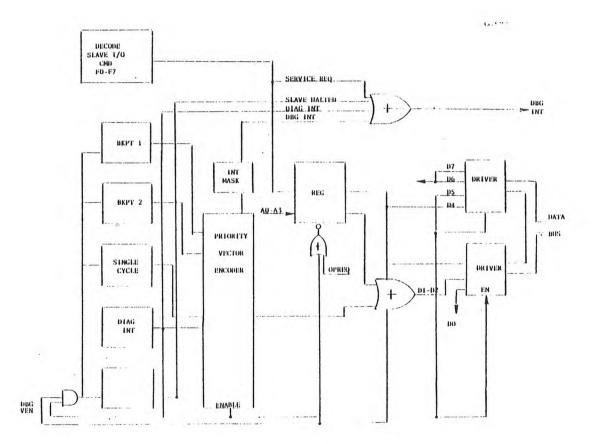

| 9-1 | DEBUG AND FRONT PANEL I/O BLOCK DIAGRAM | 9-2  |

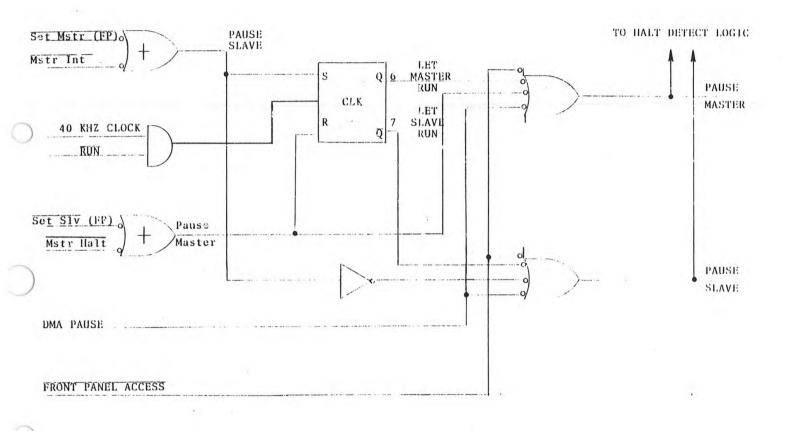

| 9-2 | MASTER/SLAVE CONTROL                    | 9-6  |

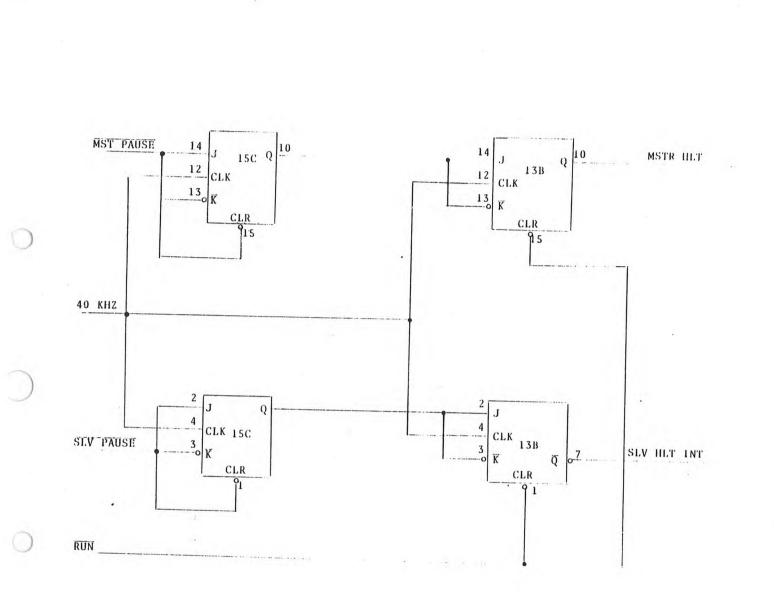

| 9-3 | MASTER/SLAVE HALT DETECTOR              | 9-8  |

| 9-4 | DEBUG I/O PORT ASSIGNMENTS              | 9-9  |

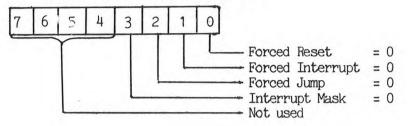

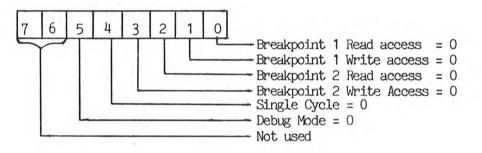

| 9-5 | CONTROL BYTE FORMAT                     | 9-9  |

| 9-6 | DEBUG INTERRUPT LOGIC                   | 9-10 |

| 9-7 | INTERRUPT PRIORITY ASSIGNMENT           | 9-11 |

| 9-8 | SEQUENCER TIMING                        | 9-13 |

#### CHAPTER 1

#### INTRODUCTION

#### 1.0 THE TWIN SYSTEM

The TWIN (TestWare INstrument) system, shown in the block diagram of Figure 1-1, consists of interdependent subsystems, each contributing to the total task of implementing user microprocessor applications from initial concept to actual hardware operation. The system closely resembles a general-purpose minicomputer during the initial stages of product development, and allows source programs to be entered, edited and assembled into object programs. Object programs may be executed simply as programs, or as part of a user's product emulation. When programs have been run and debugged to the user's satisfaction, the TWIN system is capable of programming PROM devices for inclusion in the user's prototype hardware.

The Program Development Computer (PDC) is the principal subsystem of the TWIN. The PDC employs a dual-processor/dual memory architecture operating on a common bus structure. This Master/Slave architectural concept provides the following features:

- 1. Protected operating system memory and I/O.

- 2. Complete user access to Slave memory address space and I/O address space.

- 3. Operating system and Debug software are independent of user programs.

- 4. Support of future Slave processors by adding boards and supplying additional software.

The Program Development Computer is configured using plug-in modules, each dedicated to a specific task within the system. Each module interacts with the others by use of the common bus structure. The major buses include a data bus, an address bus, and a control bus. The PDC acts as the controller for the entire system, and performs the necessary functions of transferring data to and from system peripherals.

To facilitate system operation, a dual-drive floppy disk subsystem is provided in all TWIN configurations. This subsystem, with integral controller, stores user program files and allows retrieval of these files for operation by the

C C 0

O

00

.

editor and assembler. The Signetics Disk Operating System (SDOS) software is loaded from the disk system into the development computer. SDOS provides complete control over all portions of the TWIN system.

A CRT console is the standard device for entering user programs. It is equipped with a full ASCII keyboard for data entry and a CRT display to allow the operator to view the results of his program manipulations during editing, assembly, and debug operations. The display and keyboard can be separated for user convenience. An interface is provided for an ASR-33 teletypewriter, which can be used in place of the CRT console. An optional line printer provides hard copy output.

Other system I/O devices can be added to the system to enhance its capabilities. Physical interface to the system bus is accomplished by use of the optional General-Purpose I/O card. Addition of a peripheral device requires addition of its software driver to the TWIN operating system (see Appendix D).

TWICE (TestWare In-Circuit Emulation) denotes hardware/software elements of the TWIN system that support integration and check-out of the user's prototype product. A number of different TWICE operation modes support product development, integration, and production. These are:

- 0. Using Slave memory and GP I/O, the TWIN system Slave CPU executes the user's "paper" program and allows him to determine whether or not the program does what he wants in terms of manipulating his data. The system console allows a display of the contents of memory, registers, and I/O ports to aid in locating bugs in the program. This is shown in Figure 1-2A.

- 1. Using the TWIN Slave memory for program storage and the TWICE interface cable to connect the user's prototype I/O, the system allows the Slave CPU to take the place of the user's CPU and run and debug programs. This is shown in Figure 1-2B.

- 2. Using the Slave CPU and user memory, I/O and other hardware, the system allows user programs to be run and debugged in the actual user environment. This is shown in Figure 1-2C.

The TWIN PROM programming capability lets the user program his memory with the object programs created by the system in the earlier phase of development, thus simulating 99% of the final hardware. The Debug software package lets the user trace program execution, examining contents of RAM at selected locations and checking CPU status and I/O operations. Thus the complete range of user needs is met, beginning with a user program on paper and ending with final execution in hardware.

#### 1.1 TWIN DEVELOPMENT SOFTWARE

System software provided with the Prototype Development System includes the Signetics Disk Operating System (SDOS), Text Editor, Assembler, and Debug Package.

#### SDOS

SDOS relieves the user of the necessity of understanding detailed internal operation of the TWIN. It provides complete control over operation of all portions of the Prototype Development System. All functions relating to file handling, loading and execution are monitored and controlled by SDOS, including in-circuit emulation and PROM programming functions. SDOS resides in a dedicated memory consisting of a 256 byte PROM and 16K RAM running under the Master CPU.

The SDOS software allows the user to create, edit, and assemble files; obtain object and listing outputs; load and execute programs; and, through the debug system, check out programs in an efficient manner.

SDOS provides a powerful command file capability that enables the user to create customized operating system commands.

SDOS controls the multi-drive floppy disk subsystem, a line printer, and the CRT console, which may be an ASR-33 TTY or an RS-232 compatible device. Software drivers are provided within SDOS for these I/O devices. The SDOS software provides a flexible input/output system that enables the user to dynamically assign any logical channel to any physical device or file within the system. In this way, system I/O devices may be dynamically assigned using SDOS commands either from the console or from within a user's program. Thus, the user may write his own driver for other peripheral devices and link them into the SDOS system by use of the optional General-Purpose I/O Card.

#### Text Editor

The Text Editor is a comprehensive software package that allows the user to enter and modify text files. The Text Editor is line oriented and accepts inputs from the terminal or a disk file, performs modifications in a work space, and outputs the revised text to a disk file.

#### Assembler

The Prototype Development System Resident Assembler translates symbolic assembly language instructions into appropriate machine language code.

The Assembler generates absolute object code. This code is in hexadecimal format and may be loaded into the system for direct execution or may be converted by an SDOS command to SMS format for PROM or ROM programming.

#### Debug

The Debug system is a software program which provides the user with real-time program debug capabilities within both a software and hardware environment. It uses special hardware features built into the program development system to control execution of the user's program. User programs operating under the Debug system have dynamic program trace, breakpoint capabilities, and memory modification capabilities. Status reporting on the memory, the program, and the processor is also provided.

#### 1.2 PURPOSE OF THIS MANUAL

This manual is intended to acquaint an experienced logic designer with the TWIN system, both in overall concept and architecture, and in detail. The descriptions of functions and the detailed descriptions of each board in the system should be sufficient to allow troubleshooting to the board level in case of failure. It is assumed that the reader has a knowledge of microcomputer development systems and a knowledge of the 2650 microprocessor. For a detailed description of system operation, refer to the TWIN Operator's Guide.

#### 1.3 MANUAL CONTENTS

Chapter 2 of this manual provides a description of the system in general terms, and describes its architecture. The rest of the manual is devoted to describing each board used in the system, with functional descriptions and a theory of operation at the block diagram level. System peripherals are described briefly in Chapter 2, but detailed descriptions and operating theory are not provided. The reader is referred to the manuals for each peripheral device for operation and maintenance.

#### CHAPTER 2

#### SYSTEM DESCRIPTION

#### 2.0 SYSTEM ARCHITECTURE

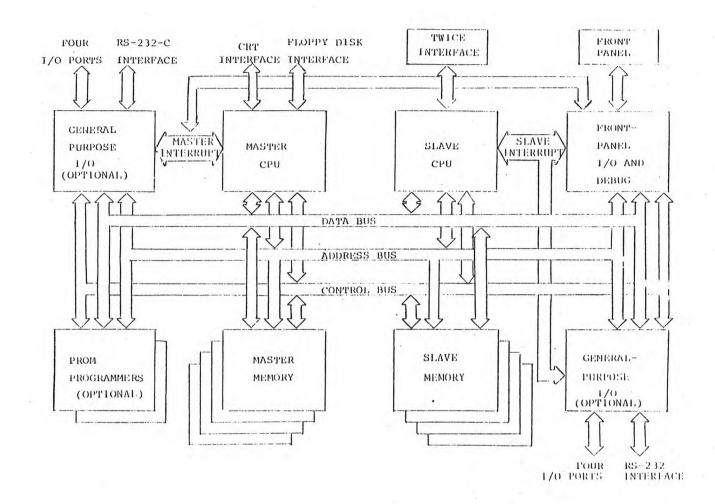

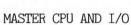

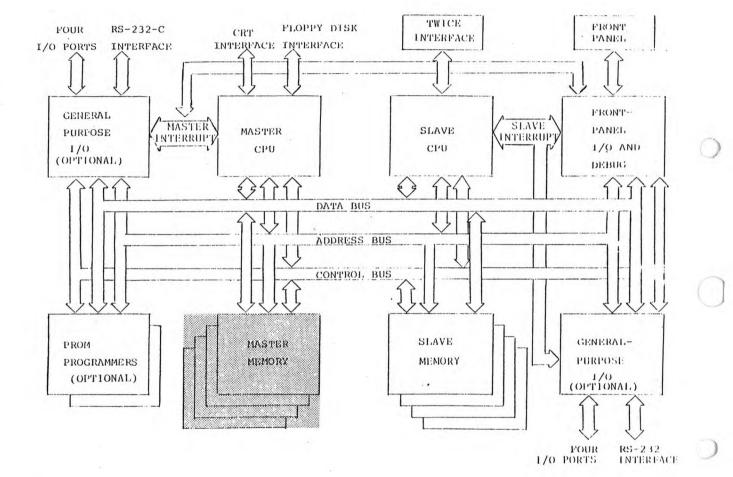

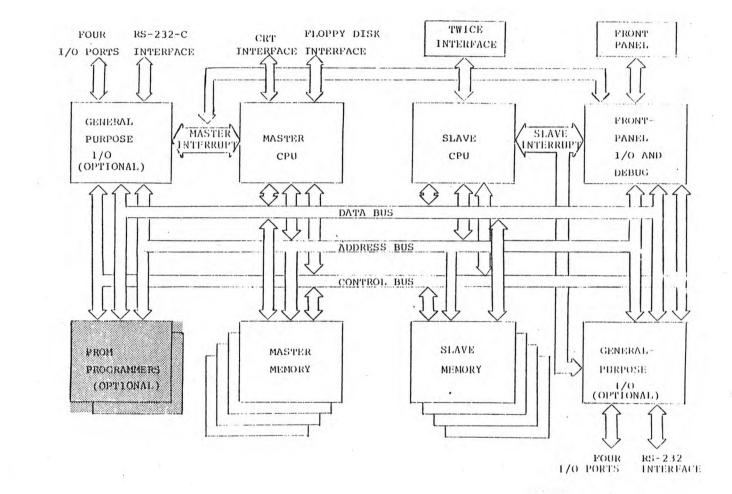

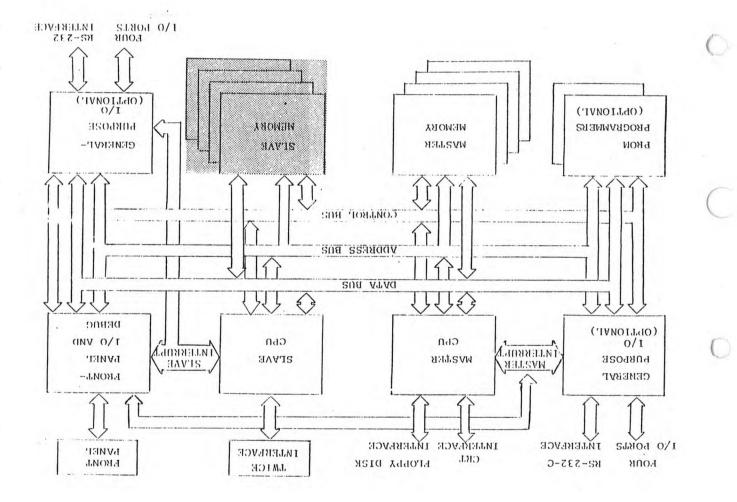

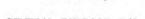

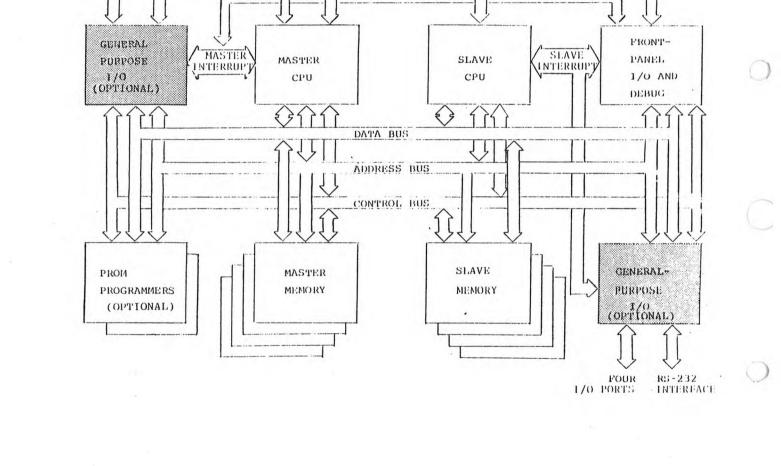

The TWIN Program Development Computer (PDC) is based on a dual processor concept, as shown in Figure 2-1. The Master CPU runs the SDOS operating system and interfaces to all system I/O devices, while the Slave CPU runs user programs as well as the Text Editor and Assembler. The Master CPU has completely separate memory and I/O, protected from user programs. This provides a relatively crashproof operating system and gives the user almost total use of the address space in Slave memory.\*

The Slave CPU can utilize the system I/O structure through "supervisor calls" (SVCs) to the Master. SVCs are described in Appendix B of this manual.

Both Master and Slave CPU's are currently 2650 microprocessor devices. However, the dual processor architecture permits different Slave CPU's to be supported by the system without requiring a complete re-write of the operating system. Only those portions of the system software unique to the Slave CPU being supported (the Assembler and portions of the Debugger) must be updated. Hardware provisions within the TWIN permit support of Slave CPU's of up to 16-bit word length and up to 64K address space.

Interaction of Master and Slave CPU's is controlled by the Debug module under Master CPU control. Both CPU's share the basic bus structure, with only one processor active at any one time. Control is transferred to the Slave by a Master halt. Control is returned to the Master by any system interrupt or a Debug interrupt such as a breakpoint.

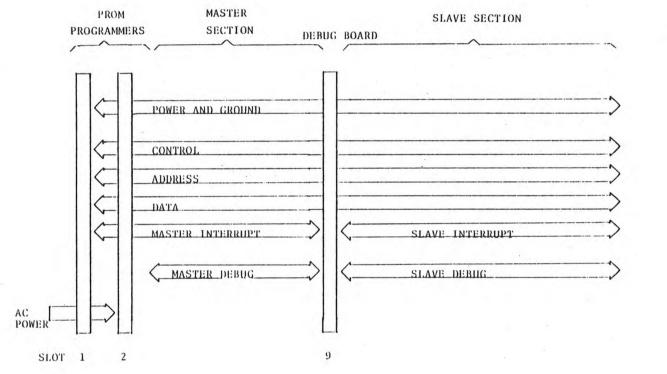

The bus structure is essentially universal for all board locations in the card cage, with minor exceptions. The Debug board splits the bus into Master and Slave halves, with a separate interrupt structure for each half. The PROM Programmer boards have dedicated locations because of the special AC voltages required for programmer operation. Memory or I/O boards may be placed in any open position (see Figure 2-3).

\* A 100 byte segment of Slave memory is required for Master/Slave interface when running the Slave CPU under Debug control.

PROGRAM DEVELOPMENT COMPUTER BLOCK DIAGRAM

The TWICE cable assembly provides in-circuit emulation of user hardware. The cable connects to the Slave CPU on one end and essentially replaces the CPU in user hardware on the other end. This gives total debugging capability in an actual hardware environment.

Basic system I/O consists of the floppy disk interface and the CRT terminal or TTY interface, both handled by the Master CPU. General-Purpose I/O modules provide a limited RS-232-C interface and parallel I/O ports to interface user peripherals. The GPI/O card can also be used in the Master side to add additional system I/O devices. Addition of a system peripheral requires addition of its software driver to the operating system. This procedure is described in Appendix D of this manual.

#### 2.1 MEMORY ORGANIZATION

Master Memory consists of 16K bytes of RAM, with the first 256 bytes overridden by a PROM which contains the system bootstrap program. When the system is initialized, the Master accesses the bootstrap program to load the operating system from the system diskette into Master Memory.

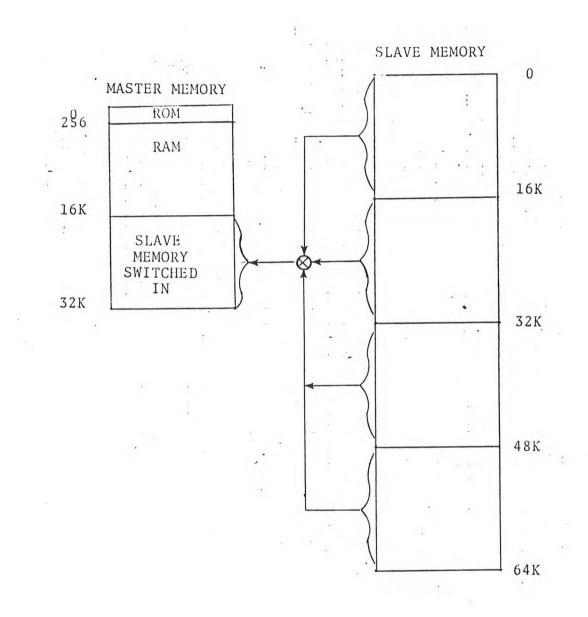

Slave Memory contains 16K bytes of RAM in the standard system, expandable to 64K bytes maximum. The Slave has access to Slave Memory only, while the Master has access to both memories. This is accomplished by assigning, under program control, a 16K byte portion of Slave Memory to the Master's 16K-32K address space. This is shown in Figure 2-2. The ability of the Master to "bank switch" Slave Memory into its address space allows communication for I/O service requests and Debug trace operation.

#### 2.2 BUS STRUCTURE

The PDC bus structure is shown in Figure 2-3. The bus is split into Master and Slave sections by the Debug and I/O Logic board. The bus is essentially universal in that data, address, and control lines are paralleled to all boards. The exceptions to this structure are Slave Debug control lines, Master Debug control lines, and special PROM power lines. The bus structure allows complete freedom of memory placement as well as freedom within each half of the bus for CPU or I/O board placement. I/O and memory address assignment is located on the indi-vidual boards.

## FIGURE 2-2

## MEMORY ORGANIZATION

#### The bus consists of 100 lines made up of the following signals:

#### COMMON BUS

#### SLAVE SIDE

16 address lines

3 Debug lines

16 data lines

3 Debug lines

2 sense/flag lines

- 21 control lines:

- 9 memory and I/O control lines

- 7 system control lines

- 8 spare lines

- MASTER SIDE 4 Debug lines

- 17 interrupt-related lines

10 interrupt-related lines

- 20 power and ground lines

- PROM PROGRAMMER

- 14 AC voltage lines

Four of the 20 power and ground pins provide an auxiliary power bus which can be connected via rear-panel terminals to an external power supply for user requirements not met by the standard system supplies. The AC voltages required by the PROM programmers extend to the end board positions only and mechanical keying prevents plugging any other boards into those positions. All board connectors are offset to prevent plugging boards in backwards.

#### 2.3 DEBUG HARDWARE

Hardware is contained on both the Debug module and Slave CPU module to facilitate the following major system Debug features:

- Master/Slave interaction

- Breakpoints

- Forced Slave jumps

#### Master/Slave Interaction

All Debug hardware communication to the Master CPU is by way of interrupts. The Master relinquishes control to the Slave CPU by performing a Halt instruction. Control is regained by the Master when it receives an interrupt. Interrupts may be from system I/O or from the Debug hardware. The Debug module contains its own interrupt priority decoder and vector generator for Debug and supervisor call interrupts.

#### Breakpoints

Breakpoint registers are contained on the Debug module. The breakpoint addresses are loaded by the Master CPU under command from the user. When a breakpoint address is identical to the current Slave CPU address, the Slave CPU is interrupted before the next instruction fetch. Both the "last" instruction address and the "next" instruction address are stored. This allows the software to examine the Slave's program and interpret op-codes for the trace printout. It also allows the system to restore the Slave to its original address after executing a register dump routine.

Forced Slave Jumps

Forced Slave jumps are required for two reasons:

- 1) To execute the user's program starting at any command location

- 2) To allow Slave execution of register dump and register restore routines for trace.

The jump address is contained in a register in the Debug module and the forced jump logic is contained on the Slave CPU module.

#### TWICE Cable

The TWICE cable allows the user to exercise his hardware while still retaining the Debug features of the development system. The cable connects to the Slave CPU on one end and plugs in in place of the user's 2650 in his hardware on the other. The cable contains line drivers and receivers close to the user end to insure signal integrity and minimize user circuit loading.

The Slave CPU essentially acts as the user's 2650. There are two in-circuit modes of operation. In Mode 1, the user's I/O is exercised while still operating out of the TWIN Slave memory. Full Debug and trace operations are available. In Mode 2, both the user's I/O and memory are utilized, still allowing breakpoints, single step, and trace. Multiplexers on the Slave board switch between the cable interface and the computer bus for each mode. The cable can remain installed in the normal Slave CPU mode with no adverse effects.

#### 2.4 I/O PROVISIONS

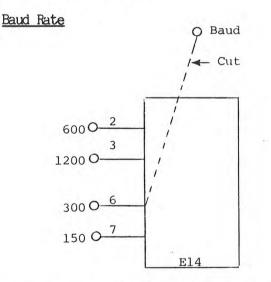

The CRT/TTY interface is a serial interface providing a limited EIA RS-232-C interface and a 20 mA TTY current loop interface. Baud rates are switch selectable for TTY (110) or CRT (300). Additional jumpers can modify the CRT Baud rate to 150, 300, 600, or 1200. A 25-pin standard EIA connector on the rear panel connects to the top edge of the Master CPU board.

The General Purpose I/O board allows both system I/O expansion and user I/O capability. The board contains a full RS-232-C interface, four sets of 8-bit parallel I/O ports, and eight interrupt flip-flops. This allows a hardware interface to any TTL-compatible peripheral. By inserting the card in the Slave side and setting a control switch, the card responds to Slave commands only and can operate the Slave interrupt structure.

#### 2.5 PROGRAM DEVELOPMENT COMPUTER SUB-ASSEMBLIES

As shown in Figure 2-1, the development computer is divided into functional modules, with each module consisting of a separate printed circuit board. The computer is divided both functionally and physically into two sections: Master and Slave. The Master section includes the Master CPU and I/O board, Master Memory (consisting of four 4K memory boards), and PROM Programmer boards. Common to both Master and Slave is the Front-Panel I/O and Debug board. The Slave section includes the Slave CPU board and Slave Memory (up to eight 4K RAM boards). General-Purpose I/O boards may be included in the Master or Slave sections. All of the boards plug into the Mother board which carries power, address, data, and control buses.

#### 2.5.1 MASTER CPU AND I/O BOARD

The Master CPU and I/O board function as the controller for the system. This board is shown in the shaded portion of Figure 2-4. The board contains clock circuitry for the 2650, which is the Master CPU, as well as for the rest of the system. The 2650 requires auxiliary logic which buffers the address and data lines to drive the system buses without loading the chip. I/O functions include I/O ports for use with the floppy disk system and the CRT terminal or TTY. Interrupt circuits are provided to interrupt the CPU during I/O operations and Debug operations. An interrupt timer, driven by the system clock, is provided to give selectable 10 ms or 100 ms interrupts. The timer can be enabled or disabled under program control.

The CPU board is the major controlling element in the system. It is the primary source of addresses for memory access and I/O operations; its control signals determine the direction of data flow on the data bus and enable the various I/O devices to receive data from or transmit data to the bus. The CPU also outputs data to and from the disk system in accordance with the disk operating system program. The following operations are performed by the CPU.

- 1) Address output to memory and I/O ports.

- 2) Data output to memory and I/O ports.

- 3) Data input from memory and I/O ports.

- 4) Control outputs to memory, I/O ports, disk, and TTY or terminal.

- 5) Operations on data input to the CPU (such as addition, logic operations, etc.)

FIGURE 2-4

#### 2.5.2. MASTER MEMORY

Master Memory, shown in the shaded portion of Figure 2-5, consists of four 4K RAM boards. A base address for each board is selected by switches mounted on the board. A portion (256 bytes) of the Master Memory is implemented as PROM, which contains the system bootstrap program.

The Master Memory is divided into three parts:

- \* The bootstrap area consists of 256 bytes of PROM which contain a program to initialize the system upon system reset. The bootstrap program also loads the resident SDOS program from the disk.

- \* The resident SDOS area contains the portion of the operating system which is always required to be resident in the system.

- \* The overlay area contains programs which are brought in from the disk as required for execution of system commands.

The memory is under the control of the Master CPU, and acts as a result of commands received from the CPU. The following operations are performed.

- 1) Output to the data bus the contents of memory accessed by the CPU

- 2) Store in memory the contents of the data bus when specified by the CPU.

- 3) Return "operation acknowledge" signals when accessed by the CPU.

#### 2.5.3 PROM PROGRAMMER BOARDS

Sec.

There are two PROM programmer boards in the system, connected to the system bus and to the front panel PROM sockets. These boards are shown in the shaded portion of Figure 2-6. Each board, although differing in detail, performs the same function. On command from the system software, an object file is loaded from the disk into Slave memory. The data contained in the file is transferred, one word at a time, from the memory to registers on the board. Sequencers and timing circuits address the chip to be programmed, and pulse the power supplies on the board to enter the data into the PROM. When the programming sequence is complete, the programmer interrupts the CPU and the next word is programmed following the same sequence. Circuitry is included to read the data stored on the PROM and output it back to the system for error checking.

When PROM programming is required, the selected programmer board interacts with the Master CPU to control the flow of data and to flag errors. The following actions occur:

FIGURE 2-5 MASTER MEMORY

FIGURE 2-6

#### PROM PROGRAMMERS

- 1) The programmer accepts data and addresses from the CPU via the data and address buses, and stores each byte in registers for programming the device.

- 2) The programmer outputs a "busy" signal during the programming cycle, forcing the CPU to loop and look for a "done" bit in the programmer status register.

- 3) The operating system checks the data programmed against the data read from the PROM after the programming cycle.

- 4) The programmer outputs a "power fail" bit to the status register when any of the on-board power supplies have failed. A "PROM Power Switch" status bit is also set when the front panel PROM programming switch is not turned on.

Circuitry on the programmer cards also allows the contents of a previously programed PROM to be compared to data in the Slave memory. The contents of a PROM may also be loaded into the memory.

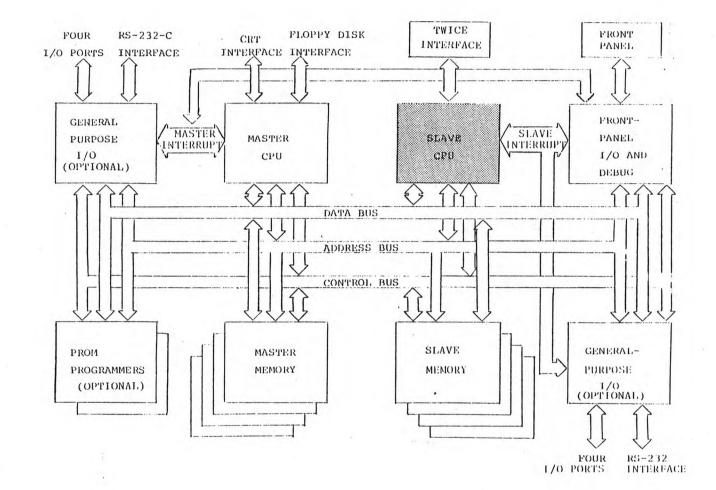

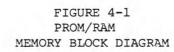

#### 2.5.4 SLAVE CPU AND TWICE INTERFACE

Control of user programs and interface to user hardware is provided by the Slave CPU, shown in the shaded portions of Figure 2-7. The board contains a 2650 microprocessor and supporting logic to drive the system bus and the TWICE interface. Jump control logic is also provided to allow the Slave CPU to jump when commanded by the system. Interrupt logic is also contained on the board to allow interrupts as requested from the Slave interrupt bus (separate from the Master interrupt bus). Priority encoding is accomplished by encoding circuitry on the board. Interface to user hardware is done by control and driver circuits which select one of three Slave CPU modes:

- 0) The Slave uses the development computer memory and I/O,

- 1) The Slave uses external user I/O and development computer memory, and

- 2) The Slave uses external user memory and I/O.

In user mode 1 and 2, the user clock provides timing for the Slave CPU.

The Slave CPU board operates in two distinct modes: under program control from user programs (either in Slave memory or user memory) to control user hardware, and under control by the Front Panel I/O and Debug board. Essentially, the types of operations performed are the same as the Master CPU, except that the Slave CPU can access only Slave Memory or user memory and I/O devices. When the

SLAVE CPU AND TWICE INTERFACE

.

Master CPU is running, the Slave is halted, waiting for control to be relinquished to continue executing instructions or to jump to an address indicated by the Debug circuitry.

Two system programs, the Assembler and the Editor, run on the Slave CPU.

2.5.5 SLAVE MEMORY

Slave Memory, shown in Figure 2-8, is similar to Master Memory, and consists of up to eight 4K RAM boards. PROM is not included. The Slave Memory holds the user program. It is also used to hold the Assembler and Editor, when these programs are run on the system.

#### 2.5.6 GENERAL-PURPOSE I/O BOARD

Interface to external data devices is provided by the General-Purpose I/O board, shown in the shaded portions of Figure 2-9. The board can be used by either Master or Slave. This board consists of four pairs of input/output ports, selected by an extended read or write operation commanded by the CPU. Each port has a unique address, and can be connected to a variety of external parallel data devices through connectors on the top of the board. A serial interface for either RS-232-C devices or a TTY is provided together with control and status ports for data interchange protocol. A UART is located on the board to perform the necessary serial-to-parallel conversion. Separate drivers are provided for either the RS-232-C or TTY outputs, although only one device can be used at one time. Clock circuits, using the system clock as a reference, provide data rates of 110 Baud for the TTY and 110 to 1200 Baud for the RS-232-C interface.

The General-Purpose I/O board accepts input data from external sources and outputs data to external sources under program control. Essentially the interaction is similar to that of memory, with the exception of the capability to interrupt the CPU when data is ready to be read or ready to be transmitted. The following are part of the interactions of the board:

- 1) Accept addresses and data from the buses and write to one of the I/O ports, including the UART status and control ports.

- 2) Output data to the CPU when a read operation is performed.

- 3) Interrupt the CPU when data is available from the ports or when data . is ready to be transmitted.

- 2.5.7 FRONT-PANEL I/O AND DEBUG LOGIC BOARD

The Front-Panel I/O and Debug Logic is perhaps the most complex board in the system in its interaction with the other system modules.

FIGURE 2-8

SLAVE MEMORY

# GENERAL PURPOSE I/O

# FIGURE 2-9

2-17

FLOPPY DISK

CRT

INTERFACE INTERFACE

RS-232-C

INTERFACE

FOUR

I/O PORTS

TWICE

INTERFACE

FRONT

PANEL

Interface to the user or maintenance front panels and control of the system during user Debug operations are provided by this board, shown in the shaded portion of Figure 2-10. The board can be broken down into several major sections which control operations independently. The first major section consists of breakpoint logic which monitors the address bus and compares the contents to the contents of the Debug breakpoint registers or to the address set on the maintenance front-panel address switches. When the two addresses are identical, control logic interrupts the Master CPU and halts the Slave CPU. At this point, the contents of memory may be examined. A second major section is Program Counter logic which is used in Debug mode of operation, where the software needs to read the contents of the Slave CPU Program Counter. Jump control constitutes the next major portion, and is activated by the system via the Master CPU. When activated, a jump address is set into the Program Counter Logic for transfer via the data bus to the Slave CPU. Master/Slave control constitutes the final major section of interest. This logic determines which CPU has control of the address, data, and control buses. Since both Master and Slave cannot have control at the same time, the control logic allows one to run and pauses the other.

FIGURE 2-10

FRONT-PANEL I/O AND DEBUG

### CHAPTER 3

### MASTER CPU AND I/O BOARD

### 3.0 GENERAL DESCRIPTION

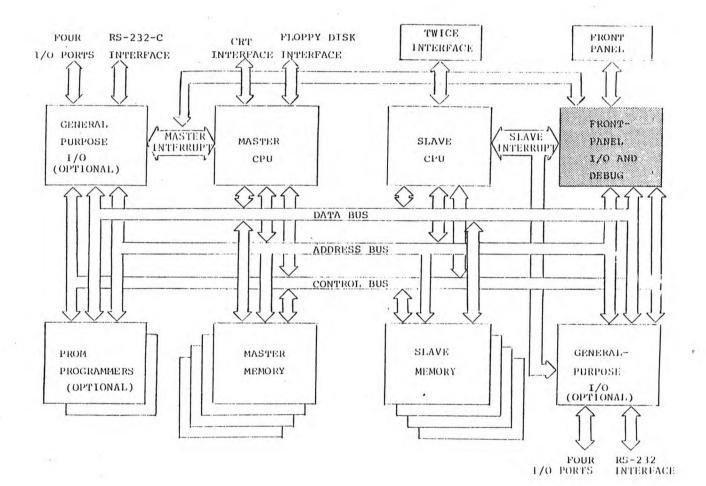

Data transfer and processing tasks, as well as overall system control are handled by the Master CPU and I/O board. In system operation, the board controls the three major system buses, and performs I/O transfers with the disk system and console device.

The central processor function is performed by a Signetics 2650 microprocessor and its supporting logic, consisting of crystal-controlled clock and bus drivers for the bi-directional data bus, the address bus, and the control bus.

This chapter outlines the function of the Master CPU and I/O board in the system, and describes the logic contained on the board to implement this function. The 2650 microprocessor itself is not described. Those readers wishing detailed information on this device are referred to the Signetics 2650 Reference Manual.

### 3.1 OVERALL BLOCK DIAGRAM

A simplified data flow block diagram of the board is shown in Figure 3-1. The board can be divided into four major sections for purposes of discussion. The first major block is the CPU itself and the supporting logic. The second section includes I/O logic for communication with the disk system and the console device. The third section consists of interrupt priority decoding and interrupt vector generation logic. The last major section consists of the Baud rate and interval timer logic.

### 3.1.1 THE CPU

The 2650 CPU is the controlling element, accessing memory for instructions and executing these instructions.

Logic surrounding the CPU device is intended to provide bus driving capability and timing for the CPU's operations. Secondary functions include Slave memory bank switching and power-on reset.

The clock consists of a 10 MHz crystal-controlled oscillator which runs continuously. The output of the oscillator drives a divide-by-eight circuit to give the required 1.25 MHz clock signal for the CPU. Part of the divider consists of a flip-flop which in turn is controlled by an external "hold" signal which

3-1 .

DATA FLOW BLOCK DIAGRAM FIGURI: 3-1

effectively puts the CPU in a hold state during master/slave operation.

The CPU's data lines are buffered by transceivers whose inputs and outputs are connected to the system data bus. Each of the address lines is buffered similarly, using tri-state drivers whose outputs may be floated to allow DMA operation in future applications.

The drivers and receivers provide the necessary system bus driving capability. When the CPU is in a "run" state, the drivers are enabled, and signals are passed to the bus or received from the bus. When the CPU is halted, the drivers are disabled and put into a high-impedance state so the buses can be controlled by external devices, or by the Slave CPU.

Logic is provided to restart the CPU upon power turn-on. When the +5 V supply comes up to its operating level, the power-on detector initiates a "reset" signal which resets the 2650 CPU and also sends a system-wide reset to the rest of the modules. This causes the CPU to fetch an instruction from location 00 in Master memory and causes the bootstrap program to be initiated.

### 3.1.2 I/O LOGIC

Communications between the system and peripherals such as the floppy disk and the CRT terminal are handled by the CPU board I/O logic. There are two separate interfaces: a serial interface for the console device, either CRT terminal or TTY, and a parallel interface for the disk system. The serial interface incorporates a UART (Universal Asynchronous Receiver Transmitter) to perform the necessary serial-to-parallel and parallel-to-serial conversion for the TTY or terminal. Status and control registers are included to provide the data exchange protocol signals required by the console device and the CPU. Interface to the disk includes lines which allow control of the optional line printer which is interfaced to the disk system.

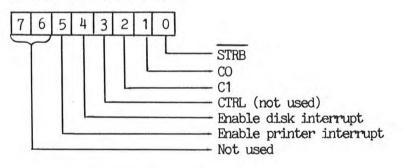

Clock generation logic provides a crystal-controlled 9.984 MHz system clock, 110 Baud to 1200 Baud TTY and CRT terminal clocks, a 38.4 kHZ I/O clock, and a 10 or 100 ms interval timer.

### 3.1.3 INTERRUPT LOGIC

Since the TWIN system operates with an interrupt-driven structure, a means must be provided to assign priority to interrupts from devices capable of such interrupts, and to generate interrupt vectors when the CPU has accepted an interrupt. The interrupt logic consists of a series of latches which are set when an interrupt occurs, and reset when the interrupt is acknowledged and the vector is output to the data bus. Priority encoders arbitrate priority among the devices requesting interrupts and enable the interrupt vector generation logic.

### 3.1.4 DMA LOGIC

Capability for future implementation of DMA boards within the TWIN system is provided by logic on the CPU board which allows the 2650 to be halted and the address and data buses to be floated. In this way the DMA boards can control the address and data buses, allowing an external device to operate directly with system memory, without utilizing the CPU and its I/O functions.

### 3.2 DETAILED FUNCTIONAL DESCRIPTION

This section describes individual logic blocks within the board.

#### 3.2.1 2650 CPU

The 2650 and its supporting logic, which will be described subsequently, provide control of the system. Acting on instructions accessed from memory, the 2650 manipulates data and provides control using its arithmetic and logic functions.

The CPU clock is generated by a 10 MHz oscillator whose output is divided by eight in two stages. The first stage divides the clock frequency by four. The second stage divides the clock by two and provides a means of stopping the clock in the low signal state for any number of half cycles. The front panel "hold" signal is generated by the maintenance front panel and stops the clock during single step or breakpoint operation. The basic 10 MHz oscillator uses a series resonant crystal as the feedback element and two inverters, which are biased into the linear region, as amplifiers. The 10 MHz output is also buffered onto the system bus for Slave CPU use.

The CPU address, data, and control outputs are buffered by a series of drivers and receiver/transmitters. Bidirectional bus drivers receive data from the system bus and transmit it to the 2650, or receive data from the 2650 and transmit it to the bus. These devices are enabled by ANDing the RUN and R/W outputs from the 2650 through inverters and gates. When the 2650 is not running (i.e., halted), the transeivers are disabled and put into the high impedance state. In this state the data bus is floating and can be driven by other modules in the system such as the Slave CPU or Debug boards.

Unidirectional bus drivers buffer the address outputs from the 2650 and drive the system address bus. Each device is enabled by an inverted RUN output from the 2650.

Control signals such as INTACK, FLAG, WRP, and M/IO are brought directly to a tri-state driver. Other signals such as RUN and OPREQ are conditioned by logic which is driven by the 2650 outputs. OPREQ is ANDed with INTACK and delayed 250 ns by an RC network. The resultant signal is squared by a Schmitt trigger and inverted before being transmitted to a driver which is enabled or disabled by the RUN output of the 2650.

### SIGNALS AND DESCRIPTIONS

ADDO-ADD15

Address lines. <u>ADDO</u> is the low-order bit. <u>ADD13</u> and <u>ADD14</u> have special <u>significance</u> for memory operations, <u>ADD13</u> is a normal address bit; for I/O operations it indicates whether I/O is extended or non-extended. <u>ADD14</u> operates normally for memory operations and indicates data or control outputs for I/O operations.

Data lines. An eight-bit bi-directional bus carrying data and instructions into and out of the processor.

This output indicates the state of the flag bit in the processor status word.

This output acknowledges that an interrupt vector must be placed on the data bus by the interrupting device.

This output signal notifies external devices that an external operation is in progress and the device performing the operation must respond with an OPACK signal (see below).

This is an input from an external device indicating that an external operation is in progress. It is input to the OPACK input of the processor to hold it in a "wait" state until the operation is complete.

INTACK

FLAG

DBO-DB7

OPREQ

HOLD

|            | SIGNALS AND DESCRIPTIONS (continued)                                                                                           |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| M/IO       | This indicates whether the operation<br>in progress is a memory or I/O operation.                                              |  |

| R/W        | Indicates whether the operation in progress is a read or write.                                                                |  |

| WRP        | This is a strobe output to signal external devices that data and address buses are stable.                                     |  |

| MSTR RUN   | This is an output derived from the processor<br>RUN output that indicates a processor run<br>condition (not halted or paused). |  |

| RUN        | same as MSTR RUN.                                                                                                              |  |

| RESET      | This is an output for system reset, occurring when +5V power is turned on.                                                     |  |

| SENSE      | This is an input to the processor SENSE line<br>to set the status word SENSE bit.                                              |  |

| INT1-INT15 | These are interrupt inputs from external devices. They are priority encoded and result in an interrupt request to the pro-     |  |

| •          | cessor and an interrupt vector being placed on the data bus.                                                                   |  |

| DBG INT    | An input from the Debug module requesting an interrupt.                                                                        |  |

| DBG VEN    | An output from the interrupt circuitry enabling the Debug vector generation circuitry                                          |  |

| MST INT O  | An output indicating that a processor interrupt has been requested.                                                            |  |

| FP HOLD    | An input putting the processor in a hold state by shutting off the clock.                                                      |  |

0

$\bigcirc$

)

$\bigcirc$

## SIGNALS AND DESCRIPTIONS (continued)

CPU CLK

A 10 MHz output from the processor clock oscillator.

- DMA PAUSE An input from external DMA devices, pausing the processor and floating the address, data, and control buses.

- CMEM Indicates that Master CPU is accessing Slave (common) memory.

## SYS CLK 9.984 MHz output for system synchronization.

I/O CLK Approximately 38 KHz output for I/O device synchronization.

When the address or control drivers are disabled, they are put in the high impedance mode and control of the buses is given to other modules in the system.

HOLD and SENSE control inputs are inverted and drive the OPACK and SENSE inputs of the 2650.

The power-on reset circuit consists of an RC network which charges during power on and a Schmitt trigger which provides a 50 ms pulse to reset system logic. The reset signal is ORed with the front panel reset signal.

For the Master CPU to access Slave memory, any 16K section of Slave memory is mapped into the Master 16K-32K address space. The 16K section is specified by two control bits in a Master I/O command. The bit formats are described in the paragraphs concerning I/O operations. When the Master address is 16K or above, address bit 14 is on. This outputs the bank switching bits to the address bus as bits 14 and 15.

Basic CPU timing is shown in Figure 3-2. Timing for Read, <u>Write</u>, and Interrupt operations is shown for reference. The system bus uses a HOLD signal rather than an operation acknowledge (OPACK). If the memory or I/O device cannot return or take data within 200 ns of OPREQ, a hold is generated by the device until the data to be read is valid, or the write data has been received. In the case of the 2102 device used in the Master and Slave memory boards, the hold duration is approximately 650 ns.

### 3.2.2 I/O LOGIC

The I/O logic on the Master CPU board provides the following functions:

- 1) TTY/CRT I/O

- 2) Disk I/O

- 3) I/O decoding

This section has a separate bi-directional I/O data bus and driver-receiver pairs to the bus. It contains all I/O decoding, I/O output storage registers, and input gating.

The I/O logic can be broken into sections for purposes of discussion. TTY and RS-232-C interfaces share the same logic, while the disk interface requires separate logic.

TTY/CRT I/O

This section provides both a limited EIA serial interface and a TTY current loop interface. However, only one terminal can be connected to the board at any time. A UART is the heart of the circuit, providing parallel to serial and serial to

a. MEMORY OR I/O READ TIMING

FIGURE 3-2 CPU TIMING

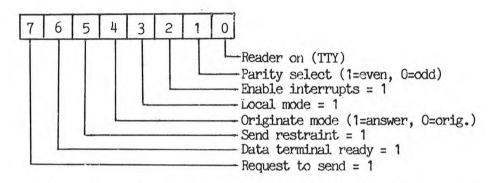

parallel conversion, status, and programmable control functions. The UART clock rate and number of stop bits are switch-selected. One switch position provides 110 Baud and 2 stop bits, while the other position provides 1 stop bit and a rate which is jumper selectable from 150 to 1200 Baud. Parity is selected under program control.

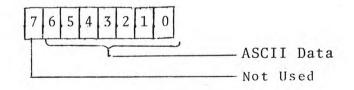

Serial data input received from the EIA receiver or the current loop interface is fed to the UART. The UART shifts the serial data in and sets the data available (DA) status when a complete character has been received. If interrupts are enabled, this triggers the TTY IN interrupt (level 4), or the RS-232 IN interrupt (level 6). The parallel data is enabled out of the UART through tri-state buffers onto the internal data bus is by reading port E8. This also resets DA.

Serial data out is transmitted by performing a write to port E8. The parallel data is presented to the UART from the internal bus and strobed into the UART by applying a pulse to its DS input. This initiates the serial output stream to an open collector driver for the TTY current loop interface and to a bipolar driver for the EIA interface. When the character is transmitted, TBMT (transmit buffer empty) is set by the UART. If interrupts are enabled this sets the TTY OUT interrupt (level 5) or the RS-232 OUT interrupt (level 7).

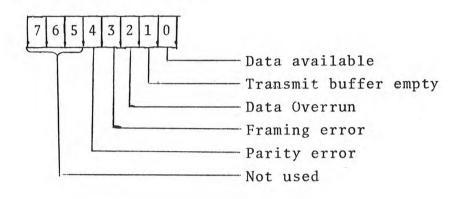

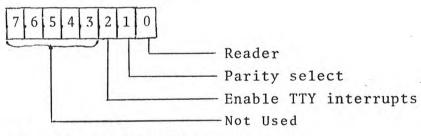

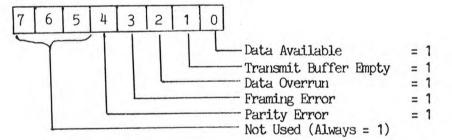

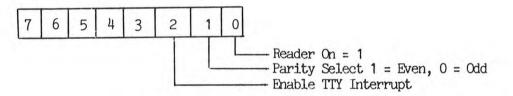

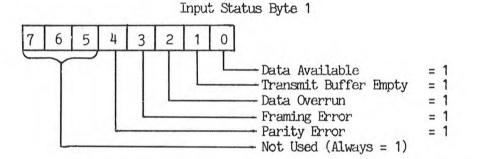

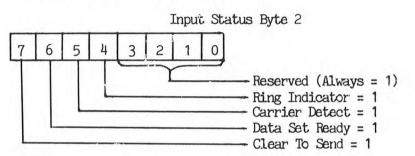

Status indications consisting of DA, TEMT, OR (overrun), FE (framing error) or PE (parity error) are available by reading port E9. Tri-state buffers enable these signals onto the internal bus from the UART. Formats for the data and control ports are shown in Table 3-1.

A TTY-related function is control of the TTY paper tape reader. A separate reader-on flip-flop and open collector driver provide the interface for this function. The flip-flop is turned on under program control and is reset upon receipt of the start bit, thus reading a character at a time.

The status byte which controls the TTY paper tape reader, the UART parity circuits, and enables the TTY interrupts is output by a write to port E9.

The TTY/CRT connector is a 25 pin connector conforming to EIA RS-232-C standards which is mounted on the development computer rear panel. This connector is connected to connector P2 on the top edge of the Master CPU board by a ribbon cable.

To interface to the CRT or other EIA peripherals, certain signals of the RS-232-C interface are pulled up permanently to a logic 1. These signals are clear to send, data set ready, carrier detected, data terminal ready, and request to send.

### CRT/TTY FORMATS

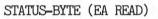

STATUS BYTE (E9 READ)

CONTROL BYTE (E9 WRITE)

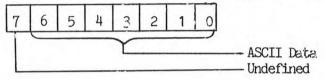

DATA BYTE (E8 READ/WRITE)

### DISK I/O

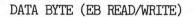

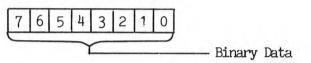

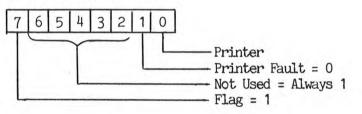

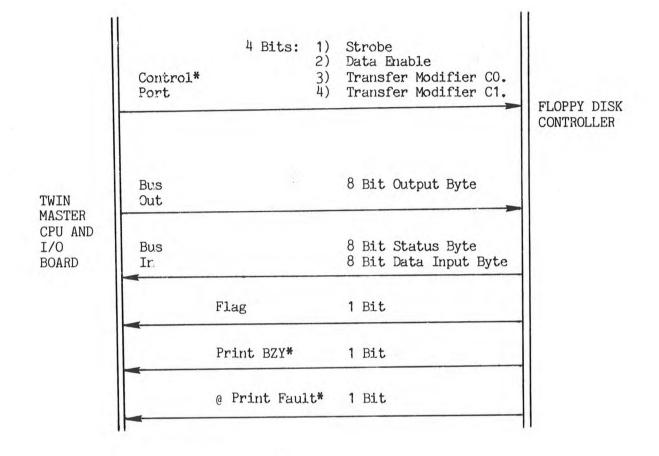

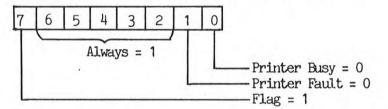

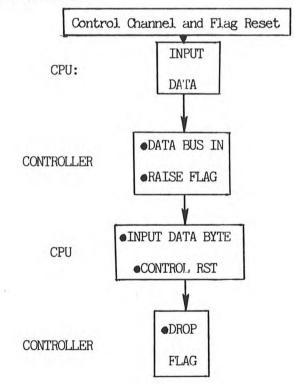

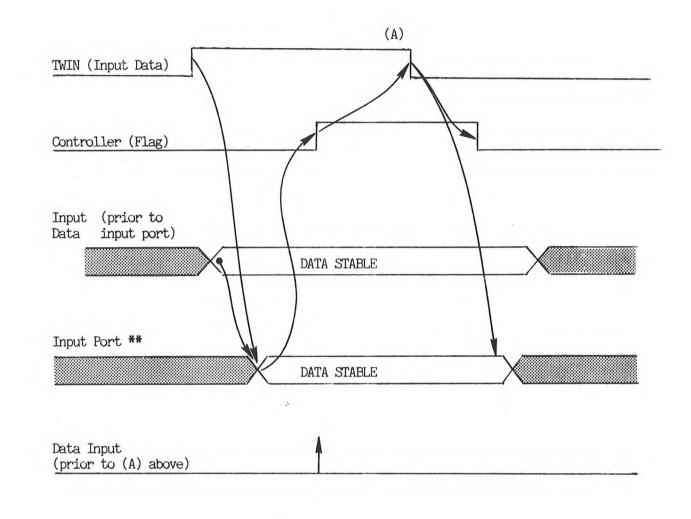

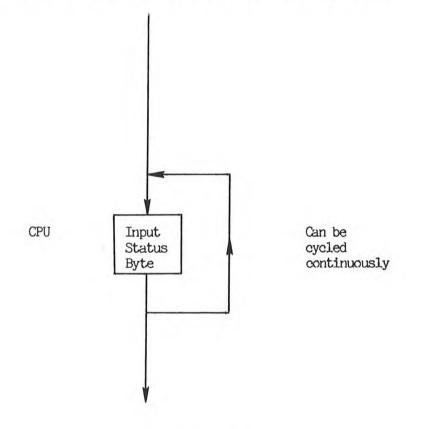

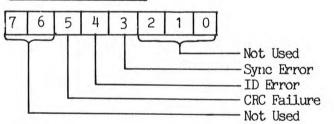

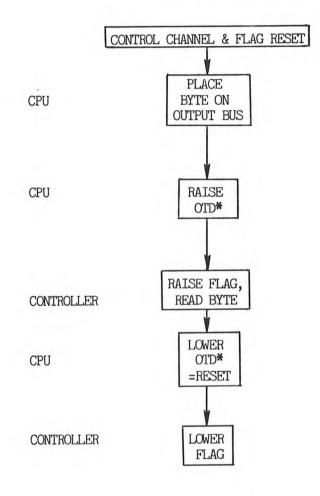

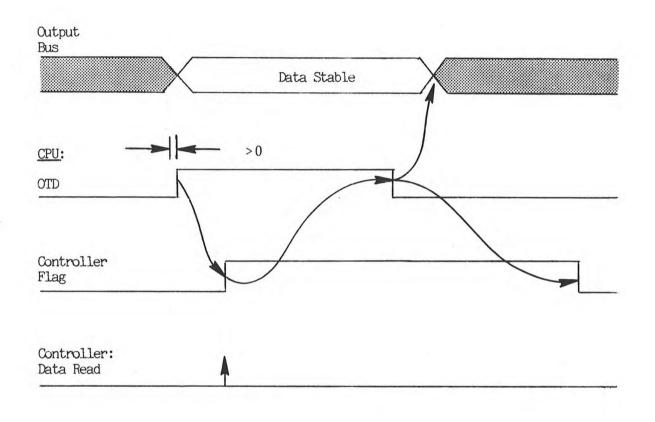

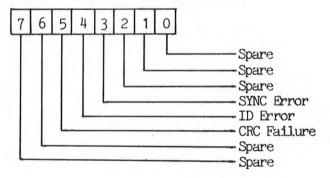

The disk I/O logic consists of a data I/O port, a control I/O port, and interrupt flip-flops. The byte formats are shown in Table 3-2. The eight disk input data bits (DIDO-7) are terminated with a pull up-pull down network and received with tri-state buffers. The buffers are gated onto the internal bus by reading port EB. Output data is stored in an eight-bit register by writing to port EB. The outputs are driven with tri-state buffers. Disk status input is enabled to the data bus with tri-state drivers by reading port EA. Disk controller signals PBZY, FLG are filtered with an RC network and shaped by a Schmitt trigger, then fed to interrupt flip-flops. A tape signal is provided only for possible future replacement of the disk drives by a high speed paper tape reader. Disk control is performed by a write to port EA. This outputs a control byte which consists of the three disk control bits, a spare output bit and interrupt enables for the disk and printer. The three output disk control bits are buffered with tri-state drivers.

For a detailed description of the floppy disk command formats and timing refer to Appendix A.

#### I/O DECODING

The I/O decoding logic recogizes extended I/O commands to addresses E8-EF. The logic provides enable lines for the tri-state input gates and clocks for the output registers. The logic also provides strobes for the bank switch and timer interrupt control discussed in other sections.

### 3.2.3 INTERRUPT LOGIC

The interrupt logic establishes priority and generates the interrupt routine address vector for 16 system interrupts. It also handles the interaction of the 16 level Debug interrupt generator.

Interrupts are stored in a dedicated interrupt flip-flop. The 16 interrupt lines are continuously sampled at a 10 MHz rate. If one or more interrupts are present, the CPU interrupt line is activated. When the CPU responds with INTACK, sampling is stopped and the interrupt address for the highest priority line present is encoded. Refer to Figure 3-2 for timing. The vector is placed on the data bus during INTACK for input to the CPU. I/O circuits can also recognize their vector on the data bus during INTACK to determine when their interrupt request has been acknowledged. On-board interrupts are reset with a vector decoder which is enabled during INTACK. The Debug module interrupts have lower priority and are given an enable line (DBG VEN) only if no system I/O interrupts.

DISK FORMATS

CONTROL BYTE (EA WRITE)

## INTERRUPT PRIORITY ASSIGNMENTS AND ADDRESS VECTORS

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Priority | Address | Function       |          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|----------------|----------|

| 2       0004       Paper Tape Rdr         3       0006       NA         4       0008       TTY In         5       000A       TTY Out         6       000C       RS-232 In       Master         7       000E       RS-232 Out       I/O         8       0010       NA       I/O         9       0012       Timer       I/O         10       0014       Printer       I         11       0016       Floppy Disk       V         12       0018       NA       I         13       001A       PROM Program 1       I         14       001C       PROM Program 2       I         15       001E       NA       I         16       0020       Slave SVC 1       I         17       0022       Slave SVC 4       Service         20       0026       Slave SVC 5       Requests         21       002A       Slave SVC 6       I         22       002C       Debug SVC 1       I         23       002E       Debug SVC 2       I         24       0030       Breakpoint 1       I |          | 0000    | Reset          | 4        |

| 7       000E       RS-232 Out $I/O$ 8       0010       NA         9       0012       Timer         10       0014       Printer         11       0016       Floppy Disk         12       0018       NA         13       001A       PROM Program 1         14       001C       PROM Program 2         15       001E       NA         16       0020       Slave SVC 1         17       0022       Slave SVC 3         19       0026       Slave SVC 4         20       0028       Slave SVC 5         21       002A       Slave SVC 6         22       002C       Debug SVC 1         23       002E       Debug SVC 2         24       0030       Breakpoint 1         25       0032       Breakpoint 2         26       0034       Single Cycle         27       0036       Halt       Debug         28       0038       Diag. Control       Hardware         29       003A       NA       30                                                                             | 1        | 0002    | NA             | T        |

| 7       000E       RS-232 Out $I/O$ 8       0010       NA         9       0012       Timer         10       0014       Printer         11       0016       Floppy Disk         12       0018       NA         13       001A       PROM Program 1         14       001C       PROM Program 2         15       001E       NA         16       0020       Slave SVC 1         17       0022       Slave SVC 3         19       0026       Slave SVC 4         20       0028       Slave SVC 5         21       002A       Slave SVC 6         22       002C       Debug SVC 1         23       002E       Debug SVC 2         24       0030       Breakpoint 1         25       0032       Breakpoint 2         26       0034       Single Cycle         27       0036       Halt       Debug         28       0038       Diag. Control       Hardware         29       003A       NA       30                                                                             | 2        | 0004    | Paper Tape Rdr |          |

| 7       000E       RS-232 Out $I/O$ 8       0010       NA         9       0012       Timer         10       0014       Printer         11       0016       Floppy Disk         12       0018       NA         13       001A       PROM Program 1         14       001C       PROM Program 2         15       001E       NA         16       0020       Slave SVC 1         17       0022       Slave SVC 3         19       0026       Slave SVC 4         20       0028       Slave SVC 5         21       002A       Slave SVC 6         22       002C       Debug SVC 1         23       002E       Debug SVC 2         24       0030       Breakpoint 1         25       0032       Breakpoint 2         26       0034       Single Cycle         27       0036       Halt       Debug         28       0038       Diag. Control       Hardware         29       003A       NA       30                                                                             | 3        | 0006    | NA             |          |

| 7       000E       RS-232 Out $I/O$ 8       0010       NA         9       0012       Timer         10       0014       Printer         11       0016       Floppy Disk         12       0018       NA         13       001A       PROM Program 1         14       001C       PROM Program 2         15       001E       NA         16       0020       Slave SVC 1         17       0022       Slave SVC 3         19       0026       Slave SVC 4         20       0028       Slave SVC 5         21       002A       Slave SVC 6         22       002C       Debug SVC 1         23       002E       Debug SVC 2         24       0030       Breakpoint 1         25       0032       Breakpoint 2         26       0034       Single Cycle         27       0036       Halt       Debug         28       0038       Diag. Control       Hardware         29       003A       NA       30                                                                             | 4        | 8000    | TTY In         |          |

| 7       000E       RS-232 Out $I/O$ 8       0010       NA         9       0012       Timer         10       0014       Printer         11       0016       Floppy Disk         12       0018       NA         13       001A       PROM Program 1         14       001C       PROM Program 2         15       001E       NA         16       0020       Slave SVC 1         17       0022       Slave SVC 3         19       0026       Slave SVC 4         20       0028       Slave SVC 5         21       002A       Slave SVC 6         22       002C       Debug SVC 1         23       002E       Debug SVC 2         24       0030       Breakpoint 1         25       0032       Breakpoint 2         26       0034       Single Cycle         27       0036       Halt       Debug         28       0038       Diag. Control       Hardware         29       003A       NA       30                                                                             | 5        | OOOA    | TTY Out        | 1.00     |

| 90012Timer100014Printer110016Floppy Disk120018NA13001APROM Program 114001CPROM Program 215001ENA160020Slave SVC 1170022Slave SVC 2180024Slave SVC 4200028Slave SVC 521002ASlave SVC 622002CDebug SVC 123002EDebug SVC 2240030Breakpoint 1250032Breakpoint 2260034Single Cycle270036Halt280038Diag. Control30003CNA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6        | 000C    | RS-232 In      | Master   |

| 90012Timer100014Printer110016Floppy Disk120018NA13001APROM Program 114001CPROM Program 215001ENA160020Slave SVC 1170022Slave SVC 2180024Slave SVC 4200028Slave SVC 521002ASlave SVC 622002CDebug SVC 123002EDebug SVC 2240030Breakpoint 1250032Breakpoint 2260034Single Cycle270036Halt280038Diag. Control30003CNA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7        | OOOE    | RS-232 Out     | I/0      |

| 10 $0014$ Printer $11$ $0016$ Floppy Disk $12$ $0018$ NA $13$ $001A$ PROM Program 1 $14$ $001C$ PROM Program 2 $15$ $001E$ NA $16$ $0020$ Slave SVC 1 $17$ $0022$ Slave SVC 2 $18$ $0024$ Slave SVC 3 $19$ $0026$ Slave SVC 4 $20$ $0028$ Slave SVC 5 $21$ $002A$ Slave SVC 6 $22$ $002C$ Debug SVC 1 $23$ $002E$ Debug SVC 2 $24$ $0030$ Breakpoint 1 $25$ $0032$ Breakpoint 2 $26$ $0034$ Single Cycle $27$ $0036$ Halt $28$ $0038$ Diag. Control $29$ $003A$ NA $30$ $003C$ NA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          | 0010    | NA             | 1        |

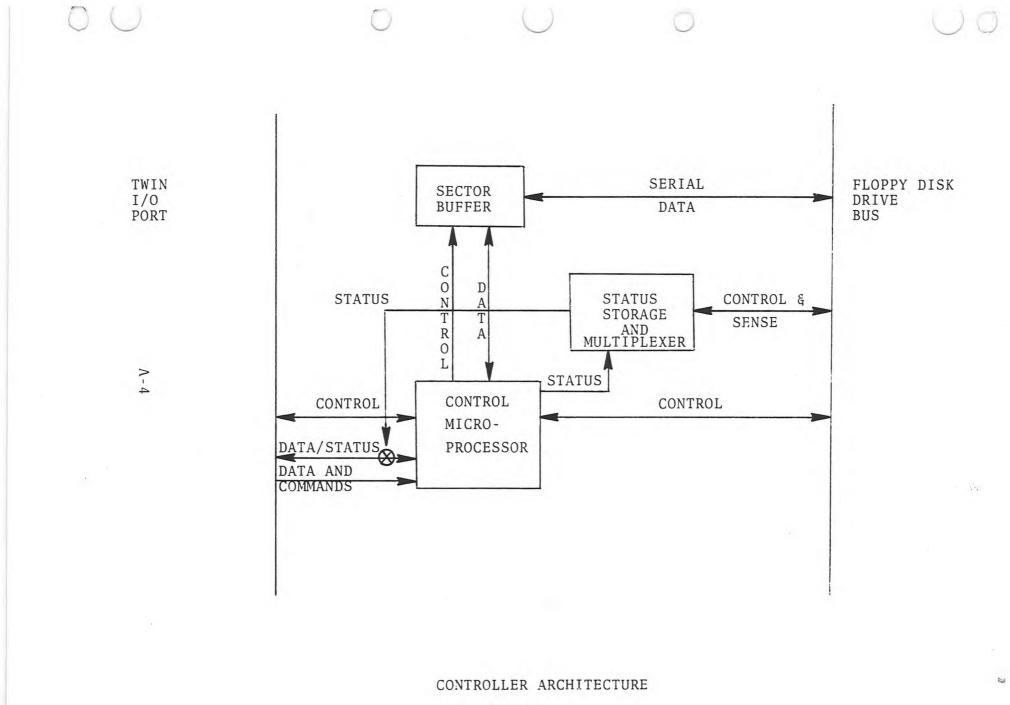

| 110016Floppy Disk120018NA13001APROM Program 114001CPROM Program 215001ENA160020Slave SVC 1170022Slave SVC 2180024Slave SVC 3190026Slave SVC 4200028Slave SVC 521002ASlave SVC 622002CDebug SVC 123002EDebug SVC 2240030Breakpoint 1250032Breakpoint 2260034Single Cycle270036HaltDebug280038Diag. ControlHardware29003ANA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9        | 0012    | Timer          |          |